Other Parts Discussed in Thread: DS90UB948-Q1,

Hi team,

My customer has the following problems, which are described in Chinese. I am not familiar with SerDes products. I translate the questions from Chinese to English. If you are confused, please point out.

At present, the scenarios used in the project are as follows:

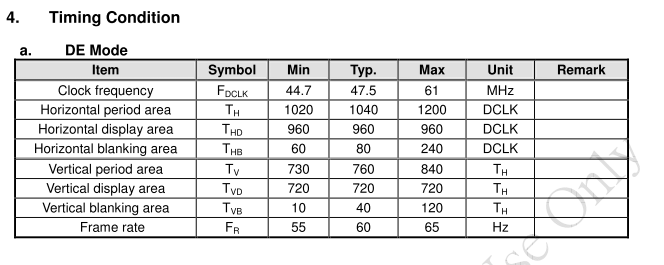

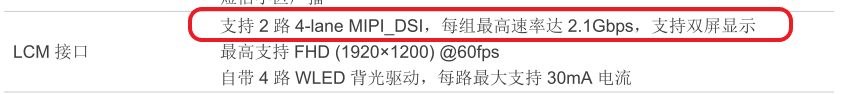

Using DS90UB941AS-Q1+DS90UB948-Q1, the display screen is dual LVDS 1920x720 resolution, the MIPI input of SOC on 941 is connected to DSI0, MIPI is 4lane, 941 and 948 direct link are Dual-Link mode.

941 uses the following configuration:

WriteI2C( 0x01, 0x82);

WriteI2C( 0x5B, 0x03);

WriteI2C(0x56, 0x01);

WriteI2C(0x03, 0xBA);

WriteI2C(0x1E, 0x01);

WriteI2C( 0x40, 0x04);

WriteI2C( 0x41, 0x21);

WriteI2C( 0x42, 0x60);

WriteI2C( 0x40, 0x04);

WriteI2C( 0x41, 0x05);

WriteI2C( 0x42, 0x1E);

WriteI2C( 0x01, 0x00);

There is no special configuration in 948, just a few GPIOs for lighting the screen.

The existing problems are as follows:

1. Test the external 85m active crystal oscillator

Test mode is configured on ds941, and test colorbar is output on 948. If 0x65 is configured as 0xc, test picture can be output normally; if 0x65 is configured as 0x8, test picture cannot be output.

When external crystal oscillator is used, DSI signal input source is used, and there is no image display on LVDS screen.

2. Test and use DSI clock source

If the clock source is configured as DSI on ds941, 0x65 is configured as 0xc or 0x8, colorbar cannot be output on 948, and the lock pin of 948 outputs a 60Hz pulse signal.

In addition, for the test picture used, the customer configured it to output 1920x720 resolution. MIPI output configuration is also 1920x720.

Best Regards,

Amy Luo