Hi,

We experience issues with the propagation of the aux_src to aux_snk signals.

The setup is a custom monitor with an internal dp input connected through a 20 cm dp 1.2 cable to a video decoder dongle.

This dongle has a xilinx virtex fpga dp 1.2 4 lanes source connected to the dp130.

All dp130 register settings are default.

The test is to powercycle the monitor and check if the link is trained.

In 10% this fails because the dp driver is unable to write to dpcd 0x600 register in the sink and the driver doesn't continue to link training.

The driver first tries to put the sink in normal power state, read the dpcd registers and read the edid before starting link training.

So if the aux communication fails, there's no active differential signal from the fpga to dp130.

When the problem occurs, we notice that we see the manchester signal on the aux_src lines and this corresponds to writing 0x600.

However, we don't see any activity on the aux_snk, so it's as if the dp130 is not connecting them.

We have verified there are no glitches on the cad_snk signal, we just have a 1M pull down connected.

So the dp130 is not in tmds mode.

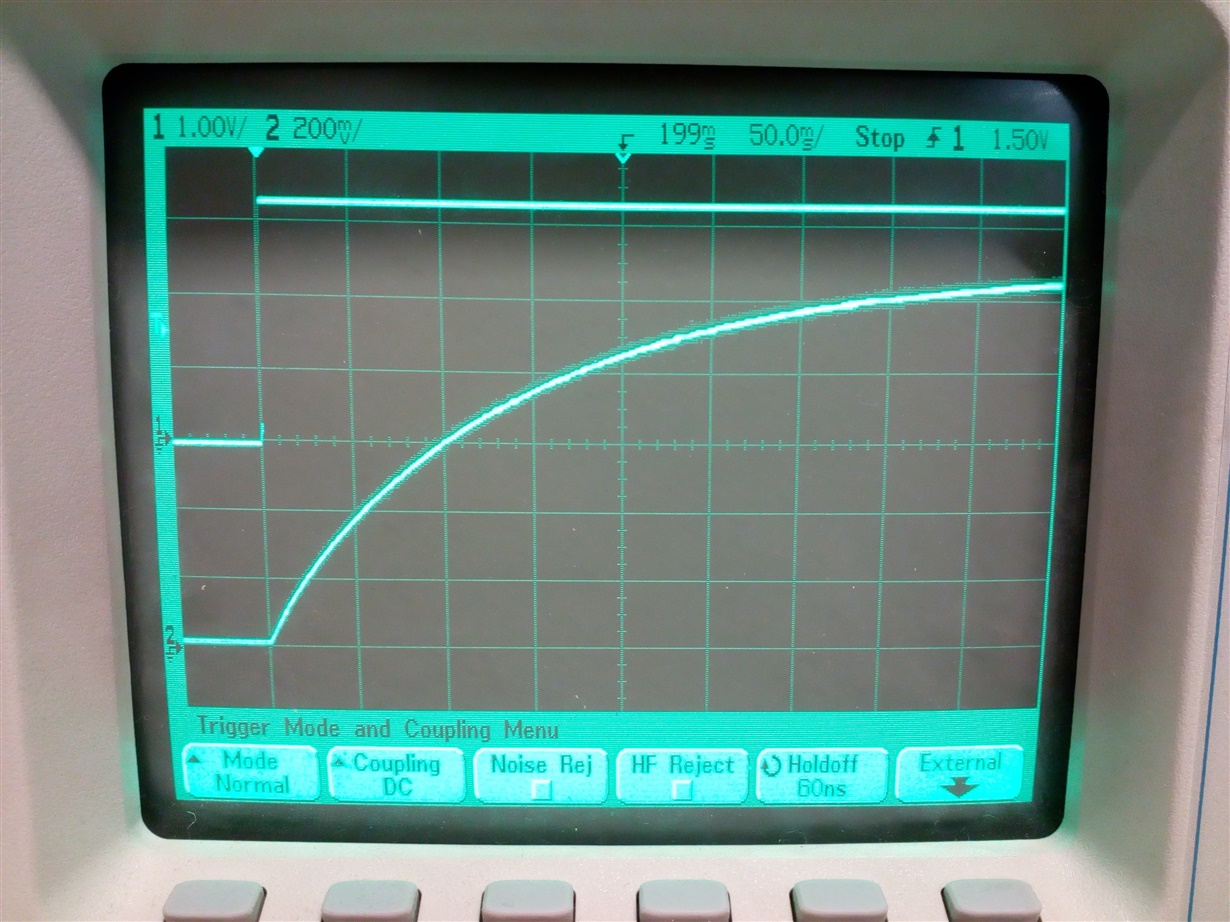

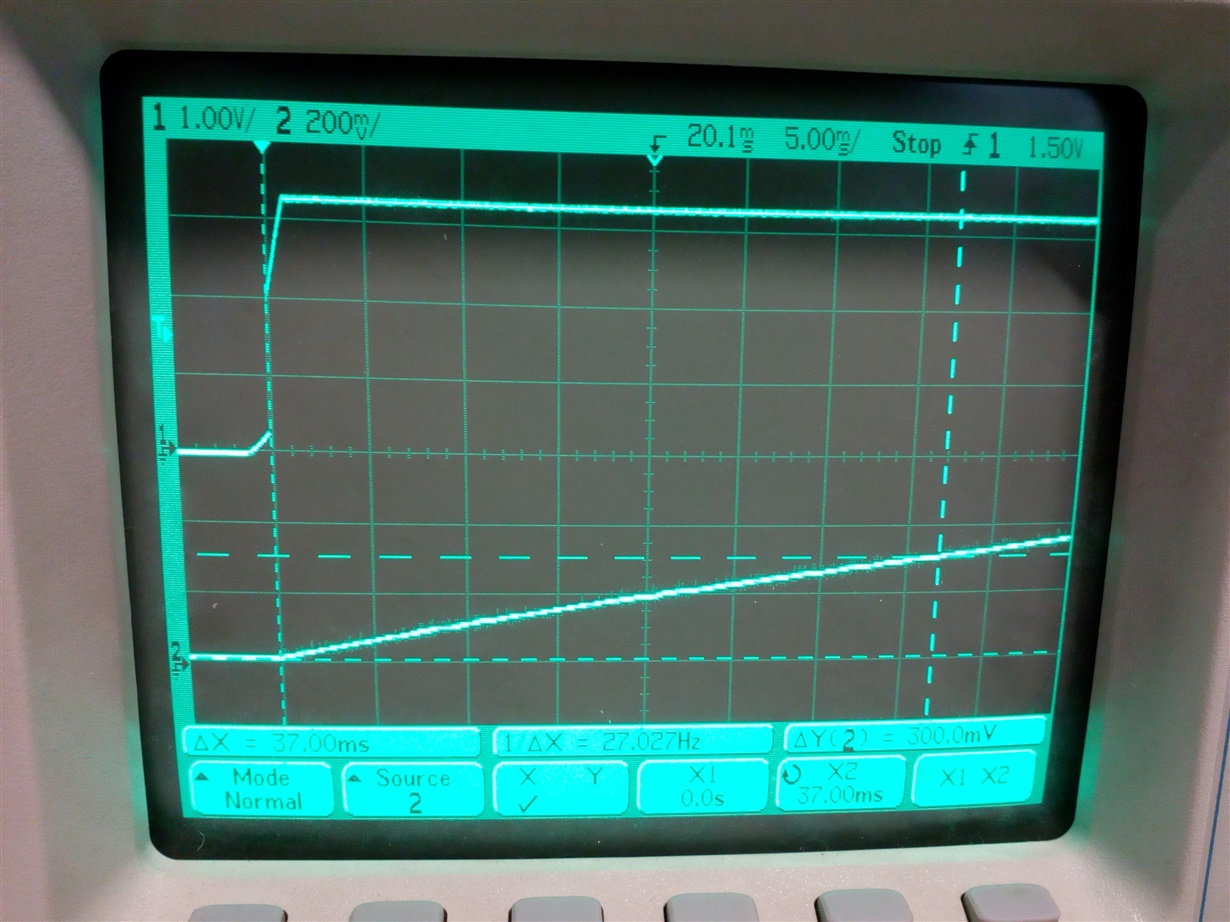

We have verified the vcc voltage and ramp up and check the rstn signal just after the voltage ramp up.

This all looks fine and in line with the datasheet.

We have tried to disable the squelch detection and autopowerdown, but no improvement.

What is strange is that the aux communication can be recovered by simply unplugging and replugging the dp cable, or even by shorting the hpd line for a few seconds.

So it's looks like the dp130 is stuck in some illegal state and is recovered by a hotplug.

We have also noticed that there are some consistent differences in the i2c register map between a good and bad powercycle:

good powercycle:

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef

00: 00 01 00 12 04 00 00 00 00 00 00 00 00 00 00 00 .?.??...........

10: 00 00 00 00 00 08 08 00 00 14 00 00 00 00 00 00 .....??..?......

20: 01 00 30 14 36 36 f0 21 00 00 00 00 00 00 00 00 ?.0?66?!........

30: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

40: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

50: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

60: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

70: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

80: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

90: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

a0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

b0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

c0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

d0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

e0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

f0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

bad powercycle:

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef

00: 00 01 00 12 04 00 00 00 00 00 00 00 00 00 00 00 .?.??...........

10: 00 00 00 00 00 08 08 00 00 00 02 00 00 00 00 00 .....??...?.....

20: 01 00 30 14 36 36 00 01 00 00 00 00 00 00 00 00 ?.0?66.?........

30: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

40: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

50: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

60: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

70: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

80: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

90: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

a0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

b0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

c0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

d0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

e0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

f0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

Notice how addresses 0x19 0x1a 0x26 and 0x27 differ.

These are all TI_TEST reserved registers according to the datasheet.

These are probably indicating what he root cause is, but unfortunately, these registers are not described in detail.

One last important thing to mention is that due to the power sequencing of the monitor, the main board is powered first and the decoder dongle seconds later.

This results in the dp hpd to be asserted already even before the dp130 is powered and the hpd remains asserted all the time.

Does the dp130 proper operation rely on seeing a hpd pulse after power up?

Thanks for your swift reply!

Br,

Bart