Part Number: PCA9306

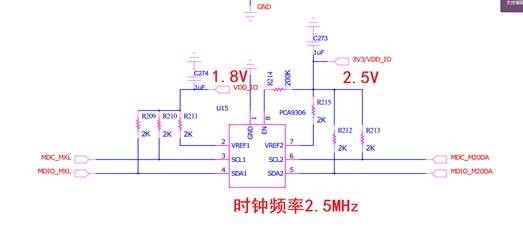

Dear TI, We are using PCA9306 to replace MAX14591, manage MDC/MDIO interface level conversion.

1. Please help to confirm the frequency range of PCA9306 (the maximum circuit frequency of 1MHz I2C bus is recommended in the specification).

2. Can PCA9306 be used as a management interface (MDC/MDIO) at 2.5MHz frequency?

PCA9306 MDC_MLX and MDIO_MLX signal many steps

PCA9306 MDIO_MLX and 1V8 signal

MAX14591 MDC_MLX and MDIO_MLX signal

3. Please help confirm whether the schematic design and the values in the diagram are OK (R215 has been modified to 200K).

Thanks for your support.