Part Number: DS90UR124

Other Parts Discussed in Thread: DS90UR241

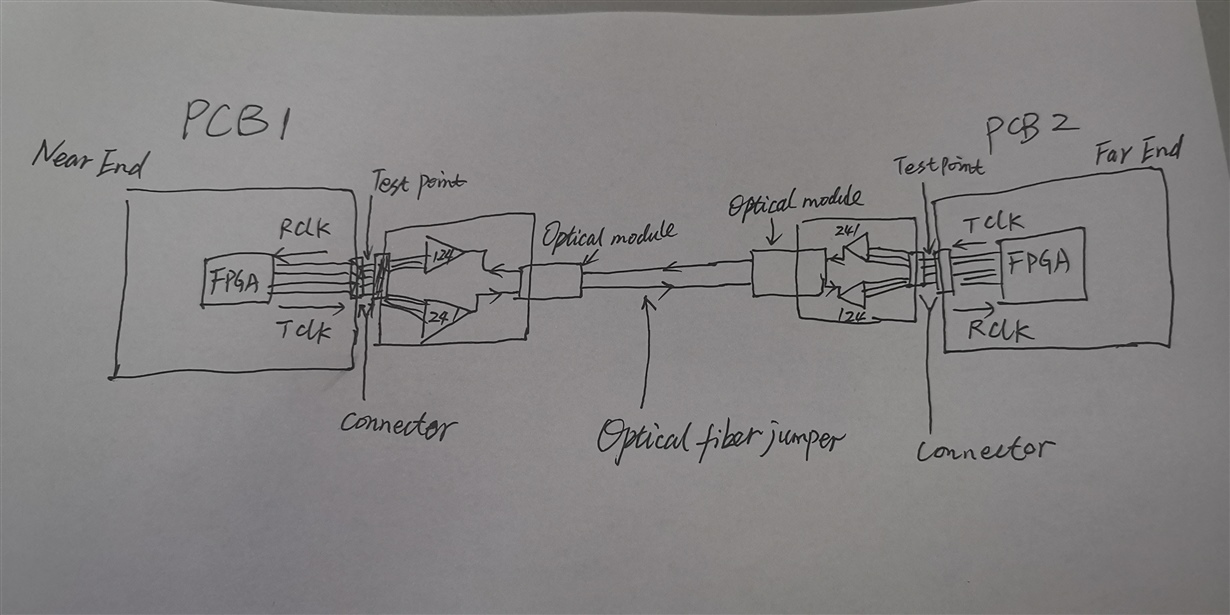

There are two chips ds90ur124 and ds90ur241 on the board, which are connected to the optical fiber module for long-distance transmission. Ds90ur124 and ds90ur241 chips are also used in the remote board card, and the optical fiber module is connected.

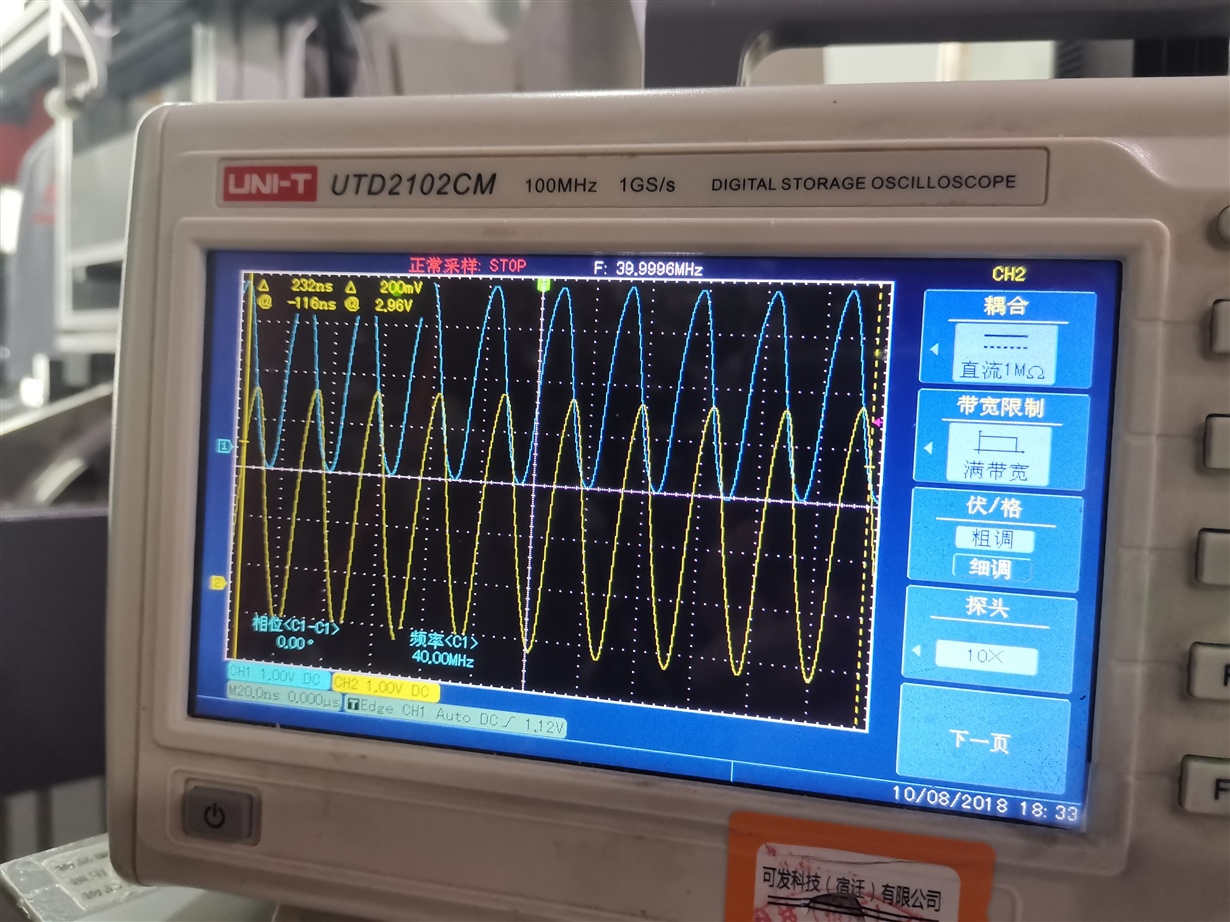

In Figure 2, the blue line is the transmission clock of 241, with the frequency of 40MHz, and the yellow line is the receiving clock of 24 pin output of 124. The transmitting clock is stable, and the receiving clock swings left and right (the period of the waveform seems to be unchanged). Because the bandwidth of the oscilloscope is 100MHz, the waveform seen is a sine wave, not a square wave.

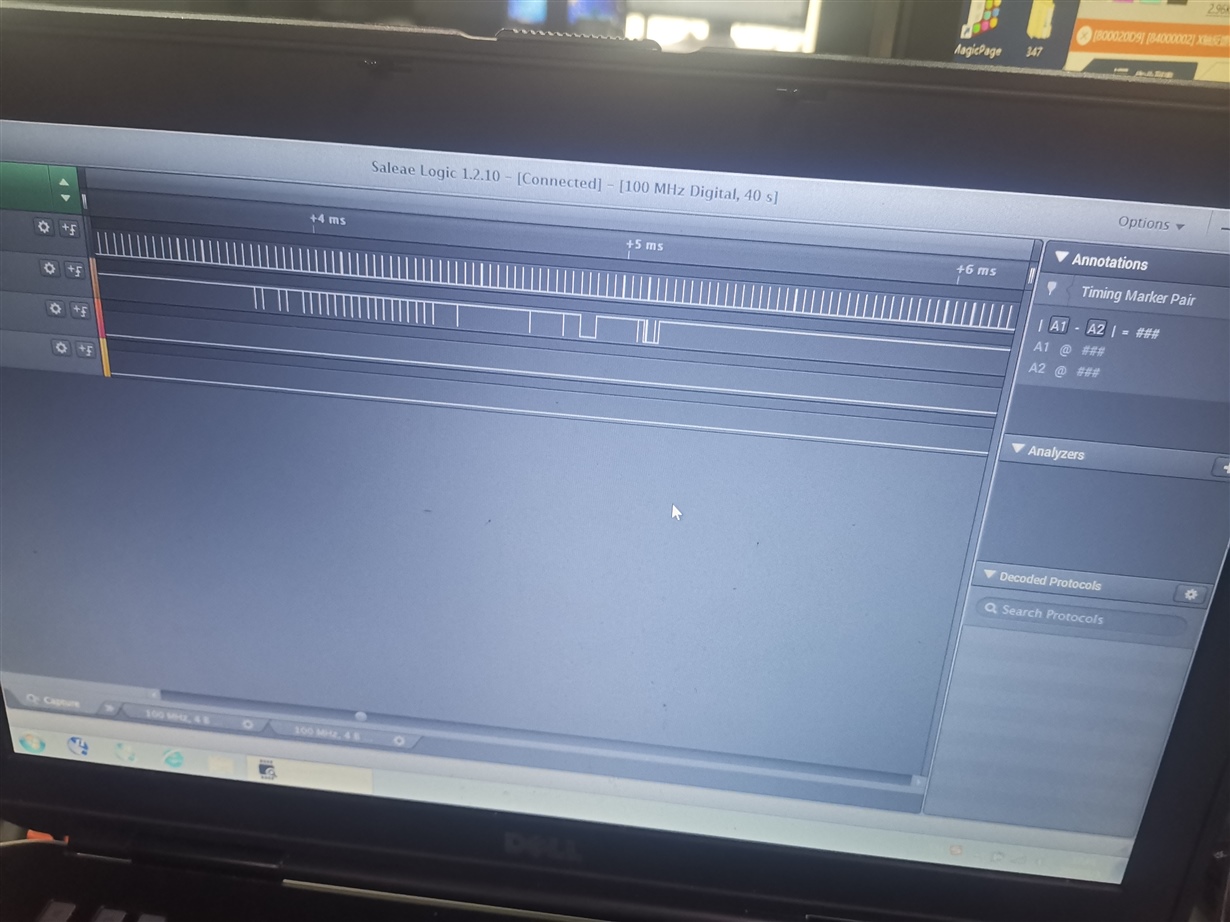

The logic analyzer in Figure 3 shows that the first signal detects one of the data lines of 241. The second signal is a receiving data line of 124。

Lock status of 124:

There are two chips on the board, ds90ur124 and ds90ur241. Lock is high when only 124 chips are working. When the two chips receive and transmit at the same time, 124 can not receive data.

1、Please help to analyze the reason.

2、It is normal to measure the sending clock with an oscilloscope, but the receiving clock of 124 shows jitter with an oscilloscope. Is it normal?