Other Parts Discussed in Thread: SN65LVDS93A, TFP401A

Hello,

we try to connect the TM101JVHP01-01 display via SN65DSI83-Q1 to the MIPI DSI interface of Raspberry Pi Compute Module 3+. Due to the post https://e2e.ti.com/support/interface/f/138/t/670554 we think that this should be possible but right now we have the problem that the test pattern isn't displayed properly as shown in figure 1

Figure 1: Test Pattern on TM101JVHP01-01

We connect a 33MHz refrence clock to the SN65DSI83-Q1 and adjust the PLL to get a 66MHz pixel clock for the display. That seems to work right, due to following facts:

- PLL_EN_STAT is set to 1 in Register 0x0A

- No Errors are shown in Register 0xE5

- And we can see 66 MHz with a near field probe on our spectrum analyzer.

- (FOR THE SAKE OF COMPLETNESS: it is also possible to adjust the pixel clock with REFCLK_MULTIPLIER in 0x0B and get the appropriate results (33MHz .... 132MHz))

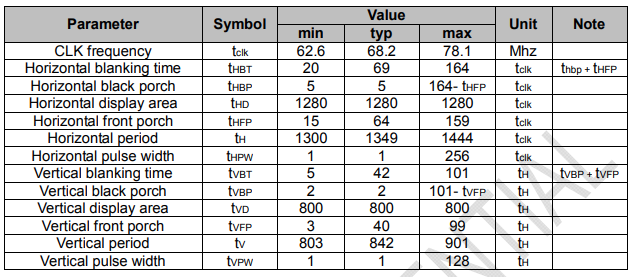

Furthermore we adjust the display timings to the typical values recommended from the datasheet (Figure 2):

Figure 2: Display Timings of TM101JVHP01-01

When we increase the Vertical Front Porch value to 255 which is out of the recommendation for the display it is possible to increase the visible test pattern on the screen slightly (Figure 3)

Figure 3: Test Pattern on TM101JVHP01-01 with increase Vertical Front Porch value

We know that the display is working correctly because we also use it in a earlier prototype on which we connect to the HDMI interface of the RPi CM3+ with the bridge combination of TFP401A and SN65LVDS93A.

Due you have any idia what causes our problem.

Regards,

J. Sarikas