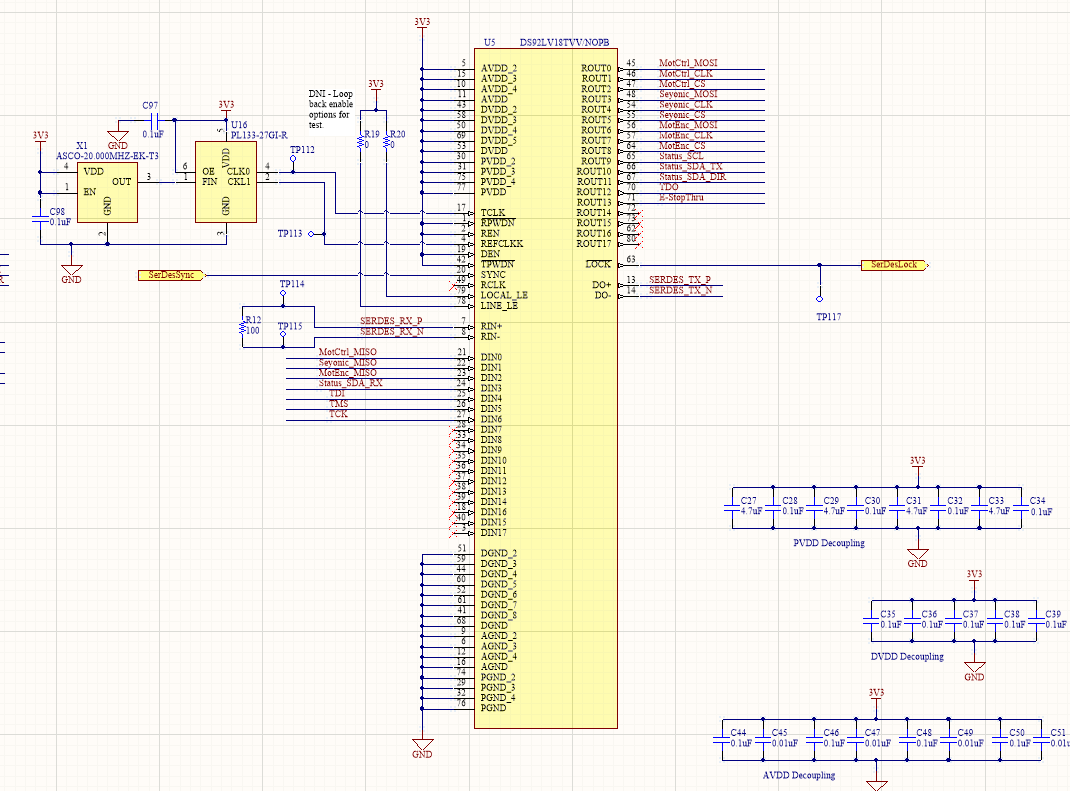

Part Number: DS92LV18

Hello,

We are using the DS92LV18 between a uC and an FPGA. I have noticed that when I hit a breakpoint on the uC and the serial transmisison stops, synchronization is lost and I have to assert the Sync bit for a second or two to get it back in sync. No problem there, that is expected. However, it brings up a fundamental question - How often do I need to be transmitting messages between the pair of SerDes devices to ensure that sychronization is maintained by the embedded sync symbols? Upon start-up, I do send the sync pattern before trying to exchange messages, but I would rather avoid sending it again if the message traffic itself can maintain the integrity of the link.

Thanks,

Jamie