Other Parts Discussed in Thread: ESD224, TPD1E05U06

Hi,

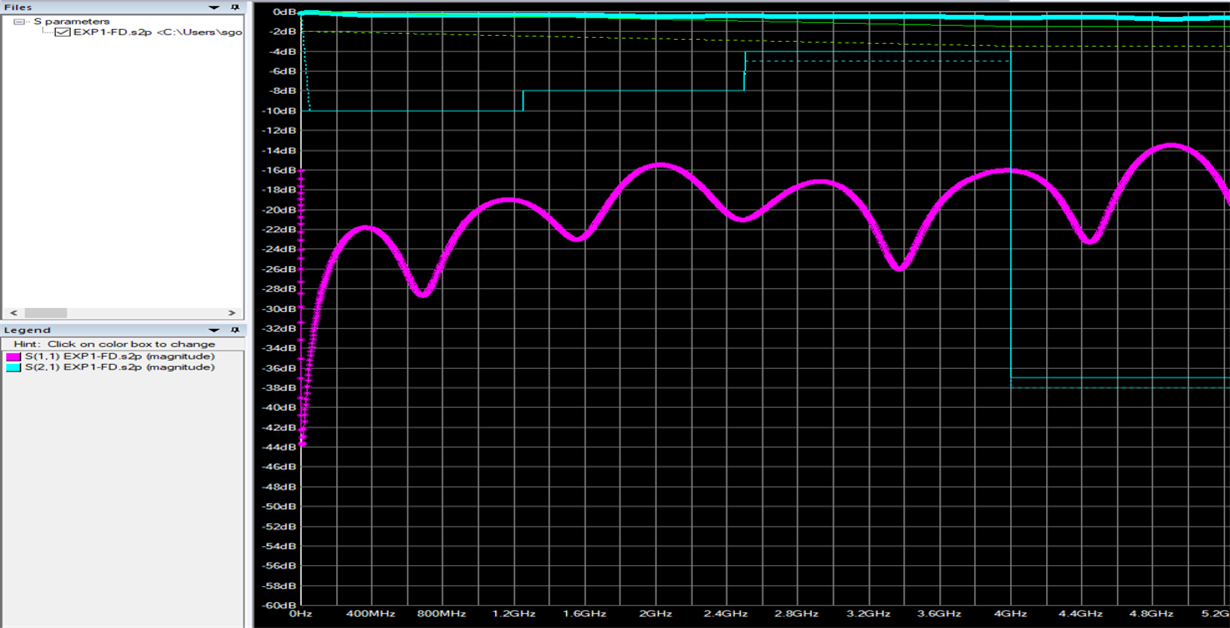

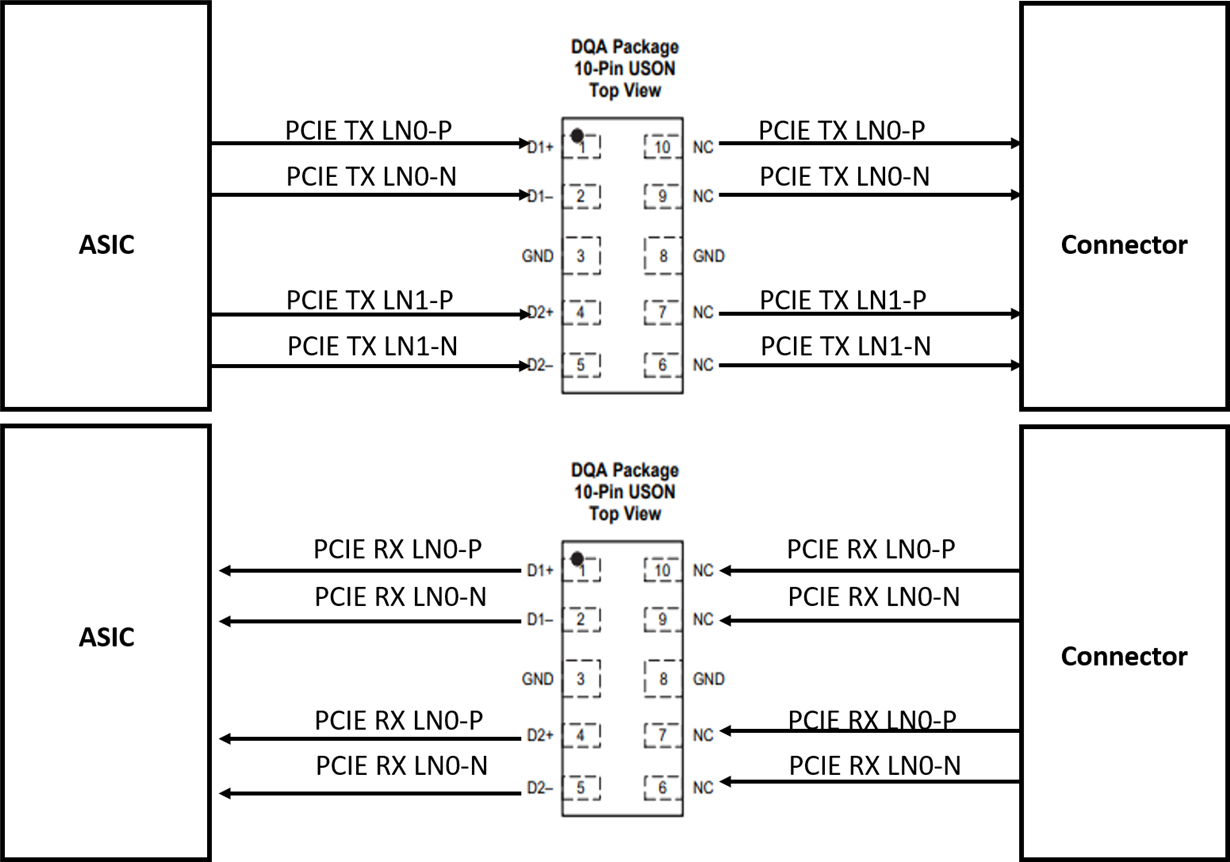

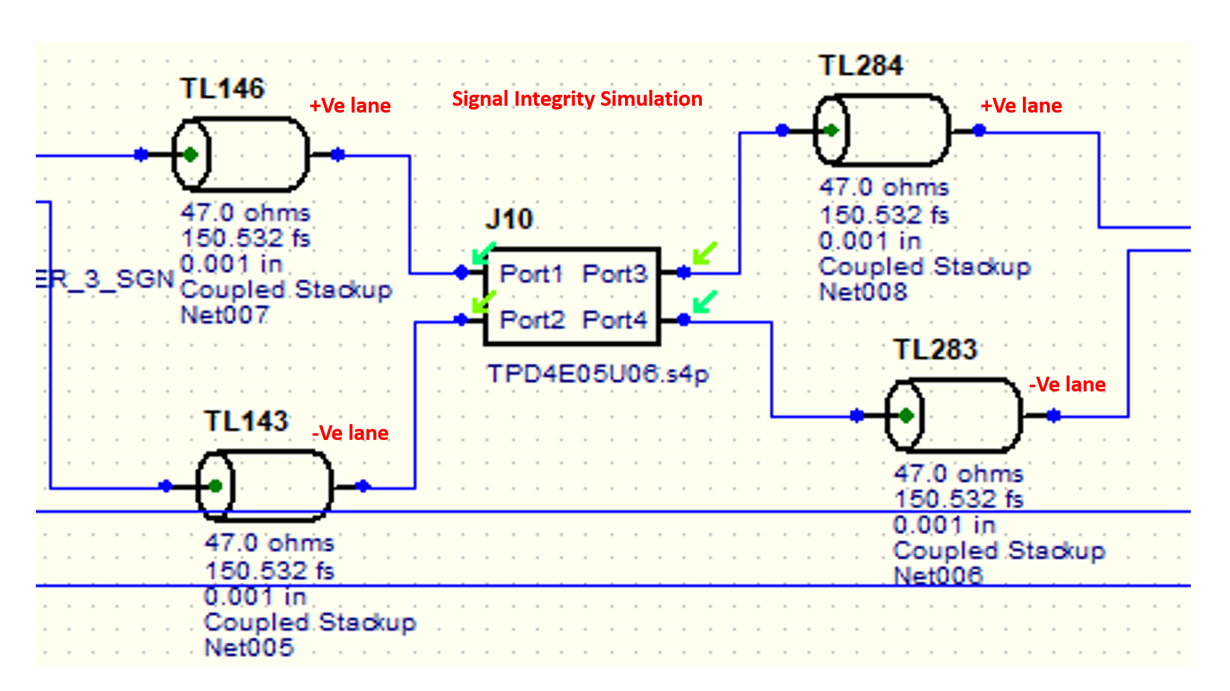

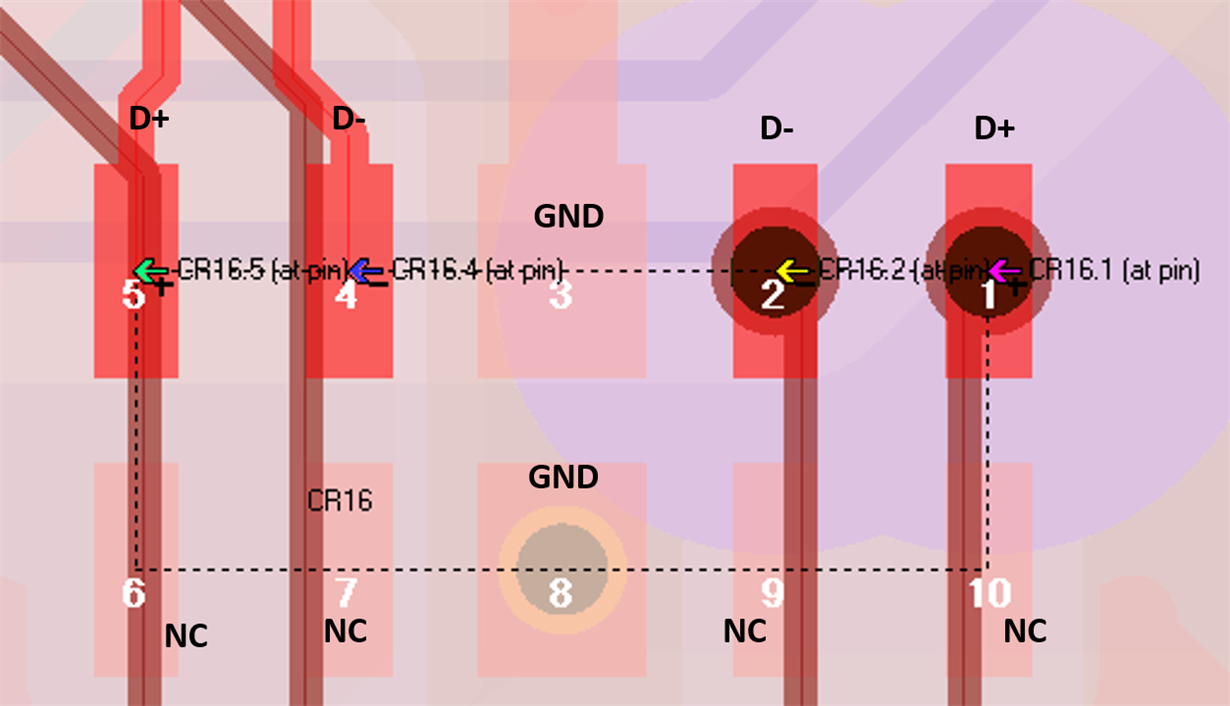

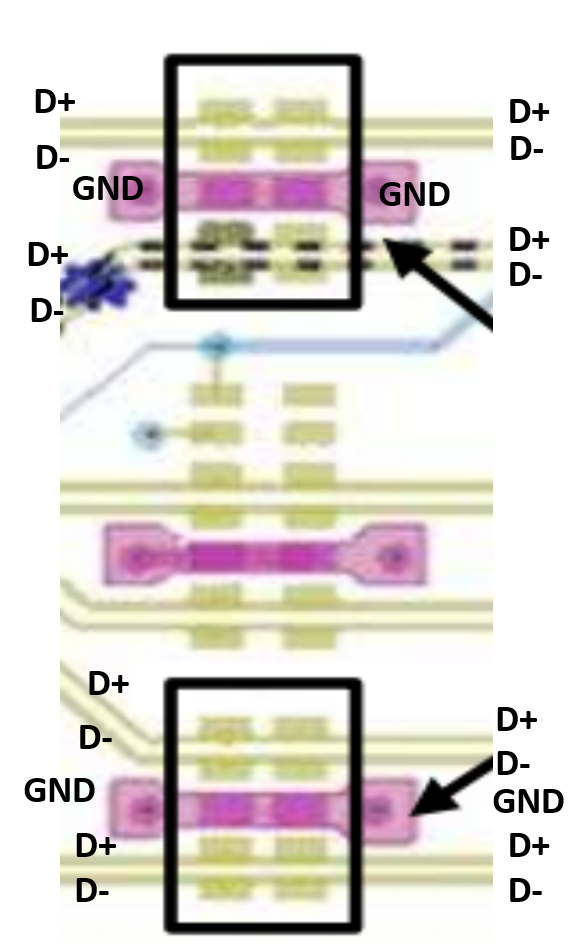

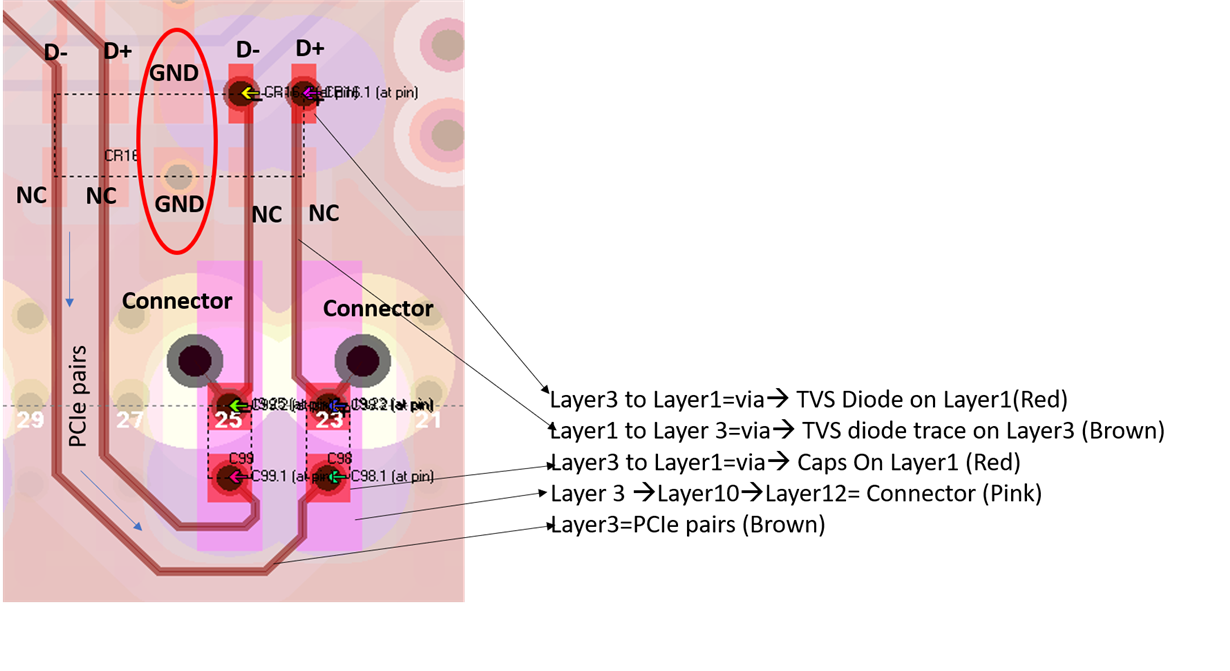

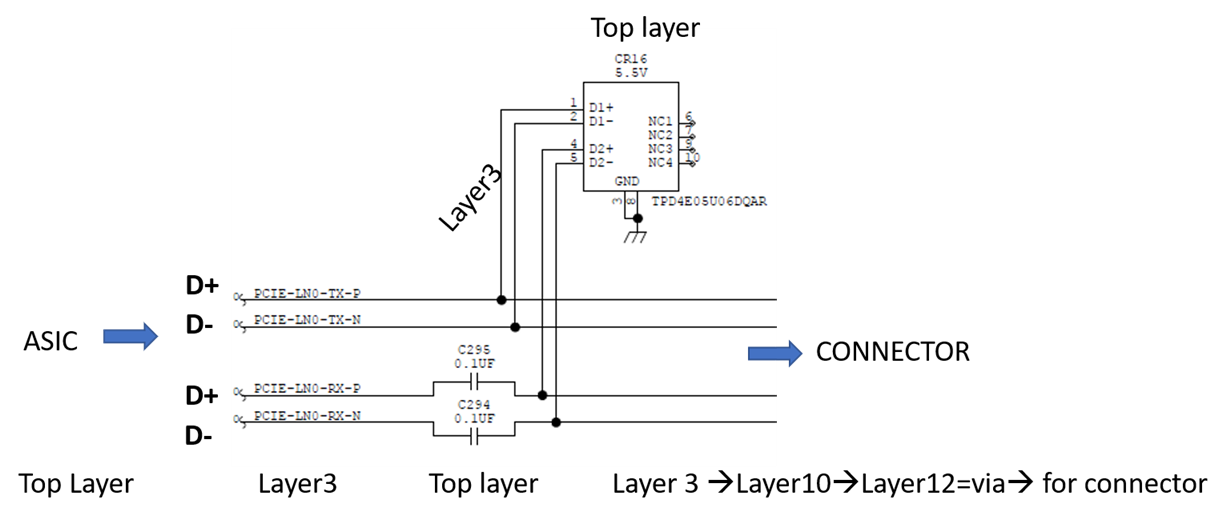

I have received the S4P file for the TVS Diode, I connected it to the PCIE +Ve and -Ve lanes. I see that strong connectivity between port 1&3 and 2&4 as shown in fig. I am confused, how do i port S-parameters to +Ve and -Ve TL's. Please find the below schematic, is it right? if not please share the port mapping for +Ve and -Ve lanes.

I read the conversation on TVS Diode port mapping it said that other end of the output should be NC but if we use in that way it is basically an OPEN.

Looking forward for the earliest reply.