Dear TI Team,

I have bought two DP83TG720EVM-MC Media Converter Evaluation Module Boards and I'm trying to build a network bridge with them.

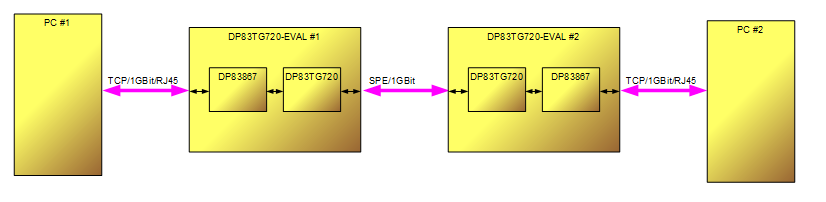

Here is a block diagram of my setup:

I want to transfer tcp/ip data from PC#1 over single pair ethernet to PC#2. Therefor I want to use the two eval-boards to make the conversion from RJ45 to SPE and back from SPE to RJ45 again.

With the default configuration of the boards I didn't get a link up with the two eval-boards directly connected over SPE. So i changed the jumper J2 from one board from master to slave and now I get a stable link over SPE. I also have a link from both PCs to the respective eval-board but I cant transfer any data from PC#1 to PC#2.

When I directly connect PC#1 and PC#2 over RJ45 I can transfer data without problems.

I have read out the debug information from both eval-boards:

Board1:

Board: DP83TG720-Q1 Media Converter Board Revision: 4 RGMII DIP Switch position: SW1:1 SW2:1 SW3:1 SW4:1 Mode: 15 Schematic Revision: 4 R Software Revision: 2.4 PHY Type 1: DP83867E PHY ID: 0 PHY Revision: 1 PHY Type 2: DP83TG720 PHY ID: 8 PHY Revision: 4 ========== Complete status report ======== +------ General status of 720 PHY -------+ | - 720 PHY is MASTER | | - 720 PHY receiver valid link | | - 720 PHY remote receiver valid link | +------ General status of 867 PHY -------+ | - 867 PHY is SLAVE | | - 867 PHY receiver OK | | - 867 PHY remote receiver OK | +-------- Link status of 720 PHY --------+ | - Link is UP | +-------- Link status of 867 PHY --------+ | - Link is UP | | - Link is FULL DUPLEX | +------ Interrupt status of 720 PHY -----+ | - UNDER_VOLT_INTERRUPT DISABLED | | - OVER_VOLT_INTERRUPT DISABLED | | - OVER_TEMP_INTERRUPT DISABLED | | - LINK_STATUS_CHNG_INT DISABLED | | - LINK_QUALITY_LOW_INTERRUPT | | - ENERGY_DETECT_INTERRUPT | | - ESD_EVENT_INTERRUPT | |----- Interrupt status of 867 PHY ------| | - PAGE_RECEIVED_INTERRUPT | | - AUTONEG_COMP_INTERRUPT | | - LINK_STATUS_CHNG_INTERRUPT | | - FALSE_CARRIER_INTERRUPT | | - MDI_CROSSOVER_CHNG_INTERRUPT | | - XGMII_ERROR_INTERRUPT | | - POLARITY_CHNG_INTERRUPT | +----------------------------------------+

Board2:

Board: DP83TG720-Q1 Media Converter Board Revision: 4 RGMII DIP Switch position: SW1:1 SW2:1 SW3:1 SW4:1 Mode: 15 Schematic Revision: 4 R Software Revision: 2.4 PHY Type 1: DP83867E PHY ID: 0 PHY Revision: 1 PHY Type 2: DP83TG720 PHY ID: 8 PHY Revision: 4

========== Complete status report ======== +------ General status of 720 PHY -------+ | - 720 PHY is SLAVE | | - 720 PHY receiver valid link | | - 720 PHY remote receiver valid link | +------ General status of 867 PHY -------+ | - 867 PHY is SLAVE | | - 867 PHY receiver OK | | - 867 PHY remote receiver OK | +-------- Link status of 720 PHY --------+ | - Link is UP | +-------- Link status of 867 PHY --------+ | - Link is UP | | - Link is FULL DUPLEX | +------ Interrupt status of 720 PHY -----+ | - UNDER_VOLT_INTERRUPT DISABLED | | - OVER_VOLT_INTERRUPT DISABLED | | - OVER_TEMP_INTERRUPT DISABLED | | - LINK_STATUS_CHNG_INT DISABLED | | - LINK_QUALITY_LOW_INTERRUPT | | - ENERGY_DETECT_INTERRUPT | | - ESD_EVENT_INTERRUPT | |----- Interrupt status of 867 PHY ------| | - PAGE_RECEIVED_INTERRUPT | | - AUTONEG_COMP_INTERRUPT | | - LINK_STATUS_CHNG_INTERRUPT | | - FALSE_CARRIER_INTERRUPT | | - MDI_CROSSOVER_CHNG_INTERRUPT | | - XGMII_ERROR_INTERRUPT | | - POLARITY_CHNG_INTERRUPT | +----------------------------------------+

I can't see any problems in the debug information.

Can you please help to determine the problem of my setup.

Thank you!

Best regards,

Peter