Part Number: DP83822I

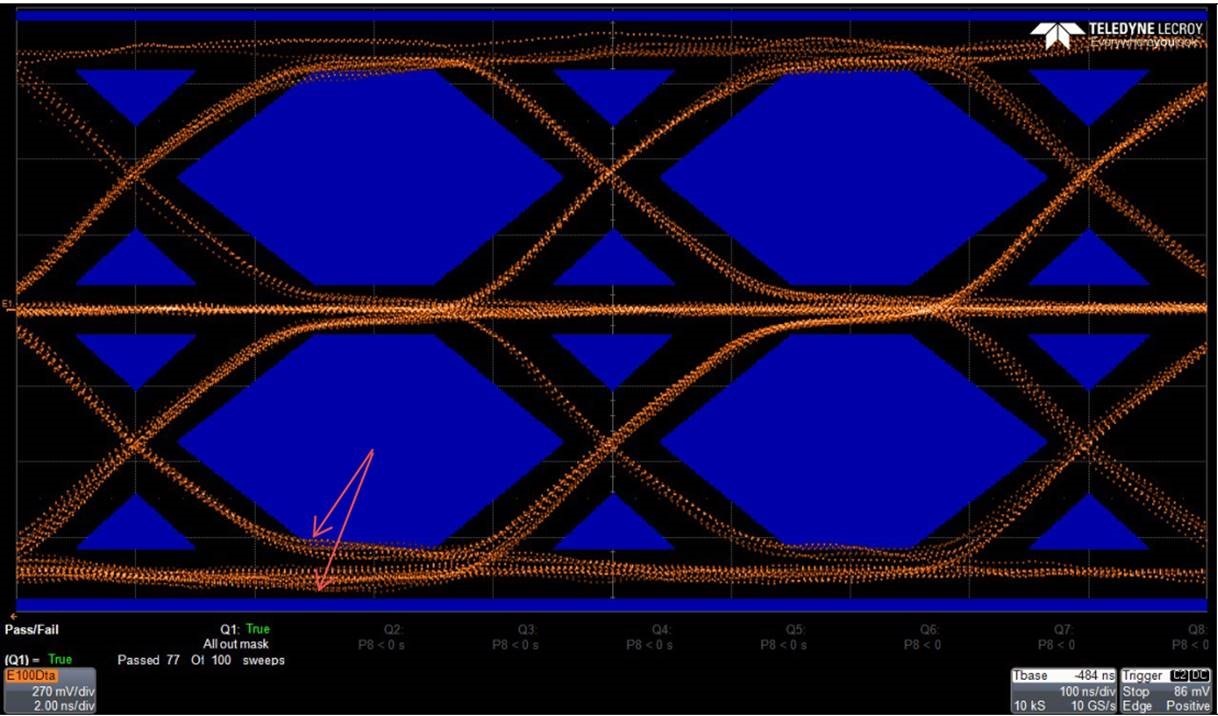

Continual discuss for the topic: DP83822I eye test failure(Twisted Pair Active Output Interface template): https://e2e.ti.com/support/interface/f/138/p/934624/3456264#3456264

We tried to short L800 but still failed;

We also optimised the PCB and FPC layout but still failed, pls. ref. to attached test report.

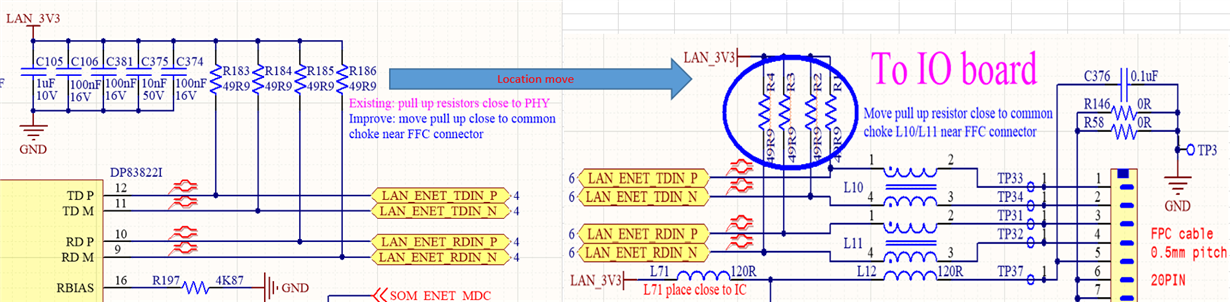

One question, what parameter causes this failure? noise on signal or rise/fall time or other parameter? can we modify 49.9ohm pull up to improve it?

BTW: we designed similar PHY circuit with another solution/IC, even using much longer FPC and PCB traces, but always get pass result;