Part Number: DS90UB948-Q1

Hi team,

My customer has been testing UB948 output jitter as attachment.

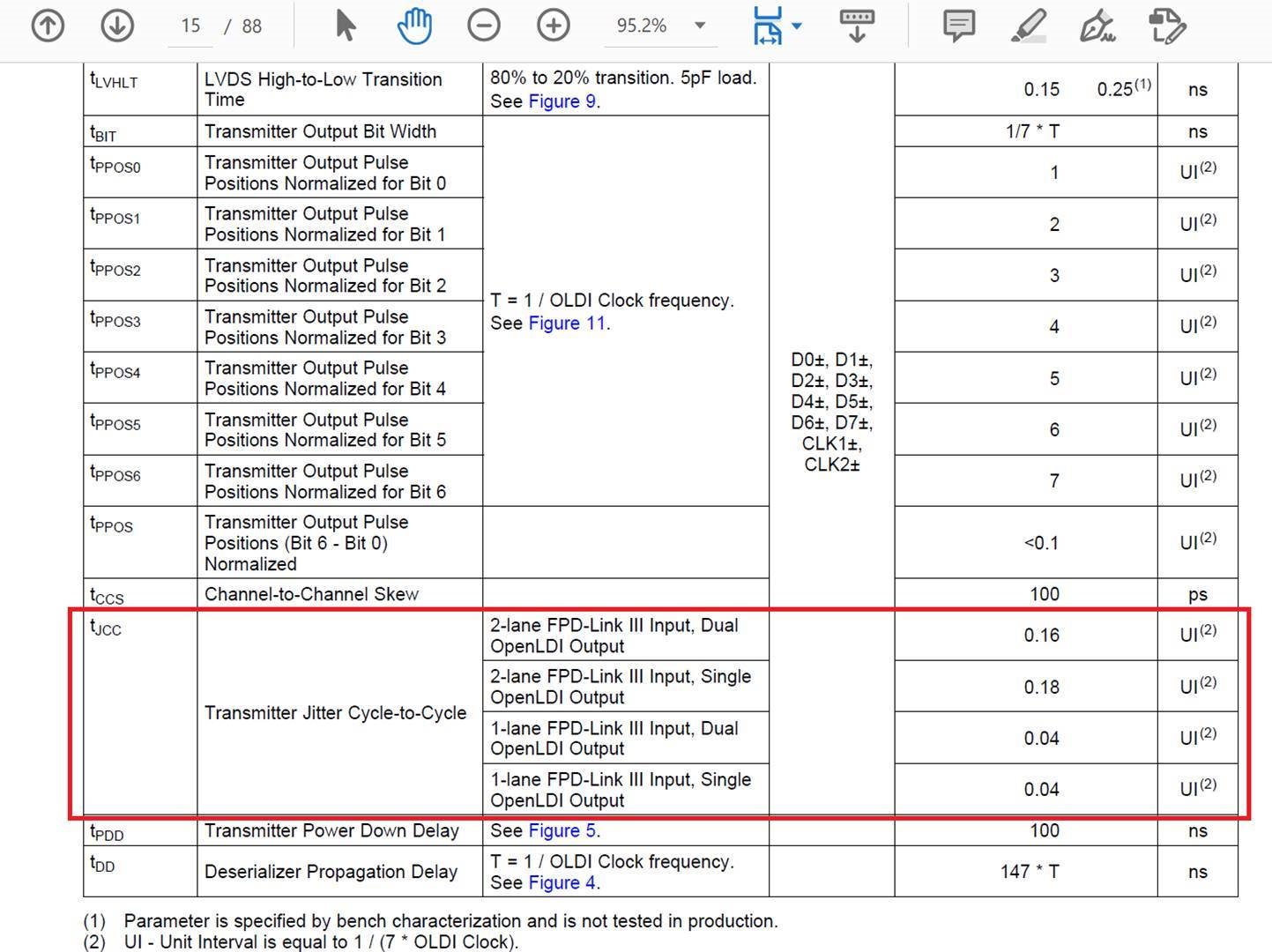

Could you please help to check if the 0.16UI is for data for clk from datasheet?

Could you also help to check the jitter is okay for the test result? (Pclk=89MHz, 1920*1080*60)

Customer is testing with 2 lane FPDlink and Dual OLDI output.