Other Parts Discussed in Thread: DP83640, ,

[Nick Saulnier]: Title & content edited Dec 15 2020 as per Anees's Dec 14 post

Hi All,

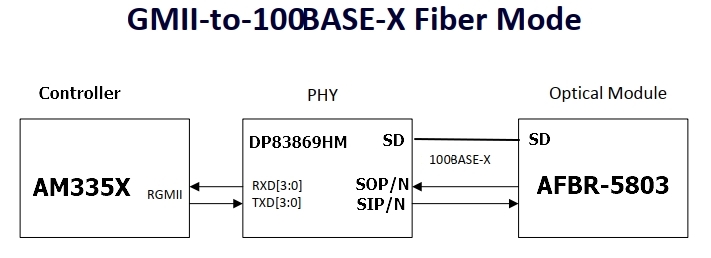

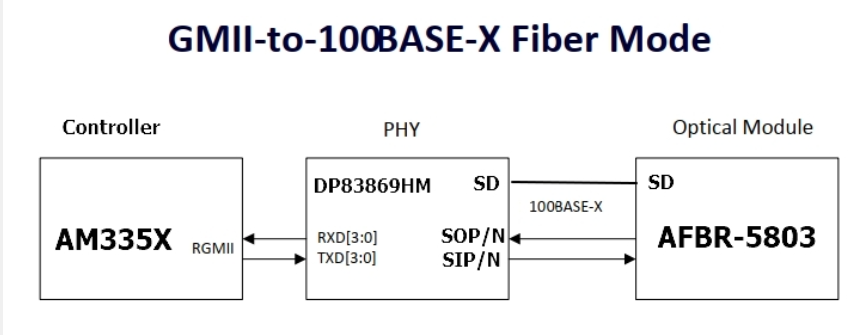

I am redesigning AM335x based OEM module to change the Brodcome PHY chip to a low-cost DP83640 DP83869 Phy chip.

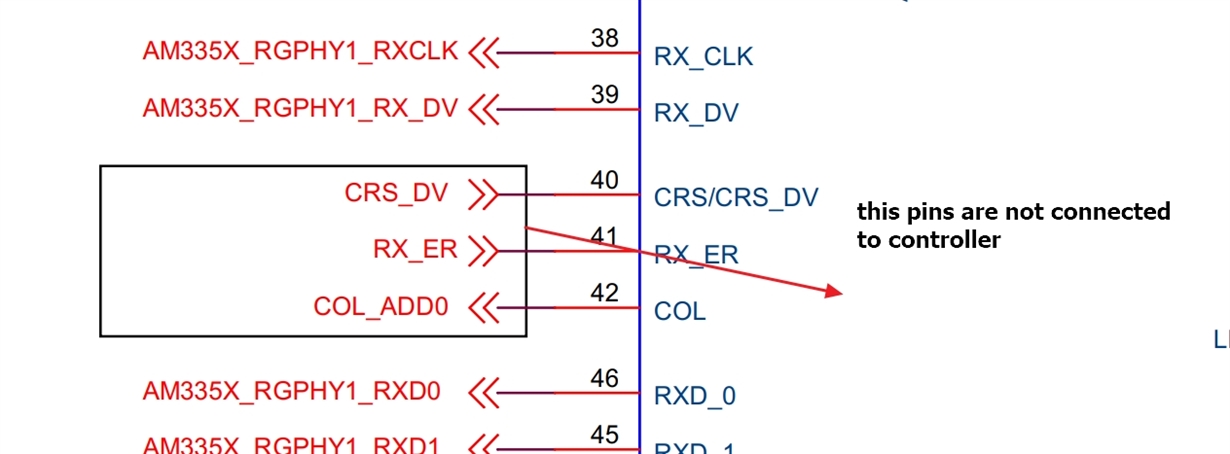

Present OEM module design, We have used dual "BCM54616S" Broadcom 10/100/1000 Phy chip with the copper interface. This Phy did not require dedicated COL, RX_ER, and CRS. So we used the COL, RX_ER, and CRS dedicated pins of the AM335x controller for some other applications.

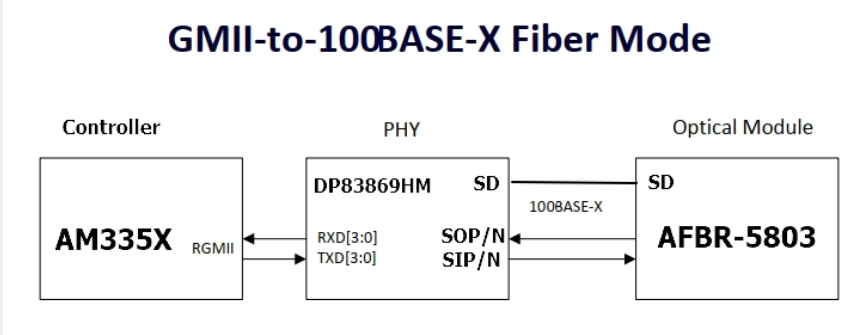

In the new design, We planning to use the DP83640 DP83869 Phy chip with a 100mbs fiber interface.

So please suggest a solution to interface the DP83640 DP83869 without COL, RX_ER, and CRS pin to the AM335X controller..

I have attached the schematic of DP83640 DP83869 with the fiber transceiver(AFBR-59E4APZ) interface.

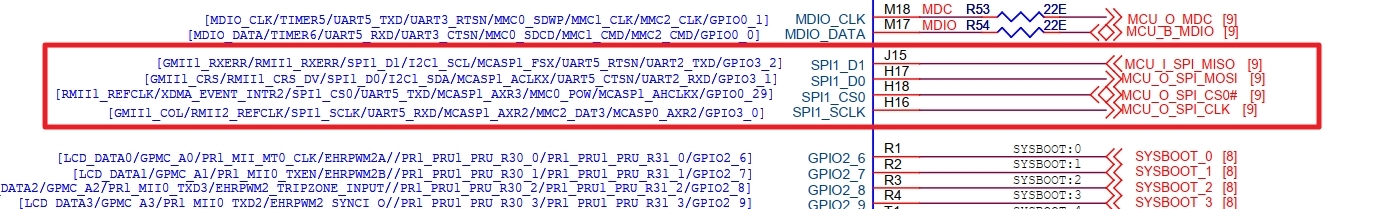

also please confirm, any option to use GPIOs or alternate pin for these functions (COL, RX_ER, and CRS) in AM335x.