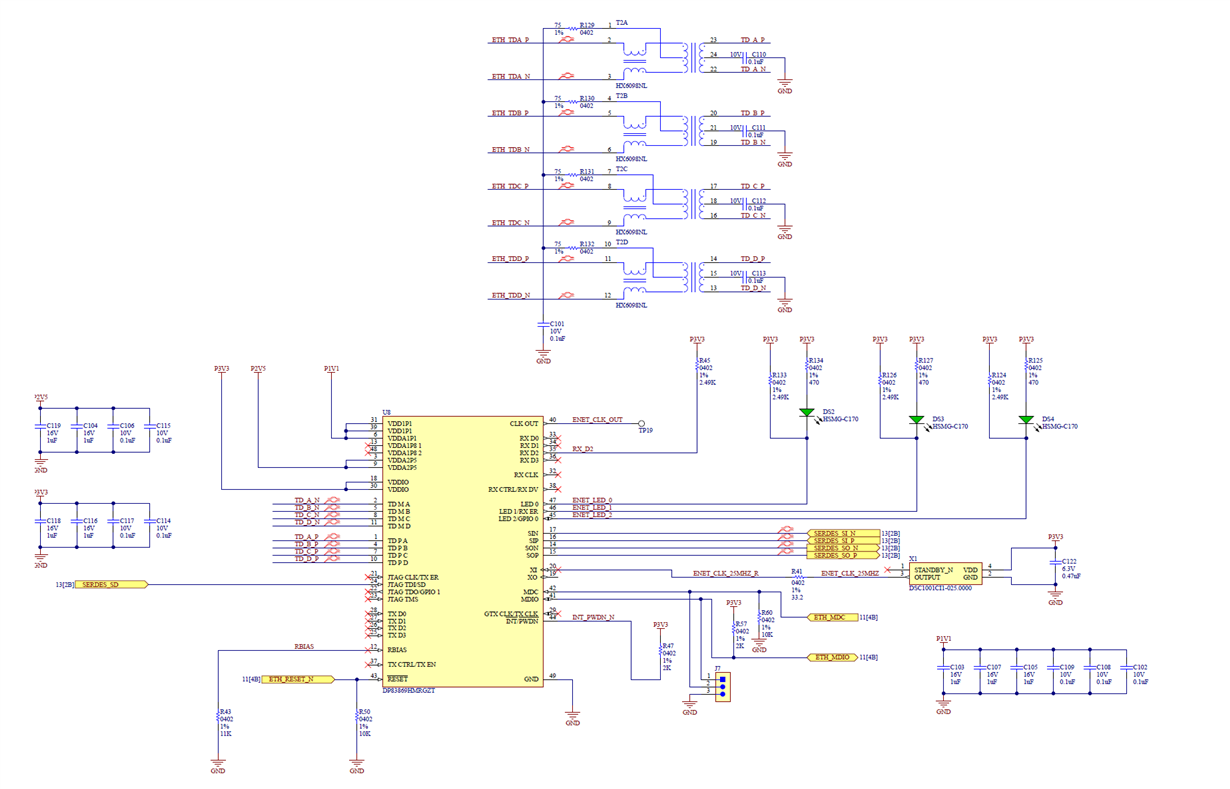

Part Number: DP83869HM

Other Parts Discussed in Thread: DP83869

It appears based on several threads that the signal detect (SD) signal is active-low (would usually be referred to as LOS instead of SD or have some active-low indication).

https://e2e.ti.com/support/interface/f/138/t/910351

https://e2e.ti.com/support/interface/f/138/t/769396

https://e2e.ti.com/support/interface/f/138/p/934072/3470807

In the third thread, Justin indicates that the polarity of the SD signal is programmable via bit 2 of register 0x30 (undocumented vendor-specific, internal configuration register). I have a design that uses a transceiver with an SD output (as opposed to LOS), missed the polarity of this signal, and could use the programmable inversion (or perhaps a disable of the SD signal) if it's available. I'm operating in the 1000M media converter mode and it doesn't appear that there is a strap or any other way to disable this signal like there is for the RGMII fiber modes. It's not clear from the datasheet, but this signal is used in media converter mode and will prevent a link if it's not correct.

I've tried the address 0x30, bit 2 approach and it seems to have no effect. Is there a way to change the polarity of the SD signal?

Thanks.