Hello,

According to the description of DSI86‘s datasheet 8.4.5.13 BPP Conversion, DSI86 could realize 24 bpp DSI input to 18bpp eDP output.

But our customer met the questions during BPP conversion, he has tried the color bar test and has no problem, but when he tried to configure as below,

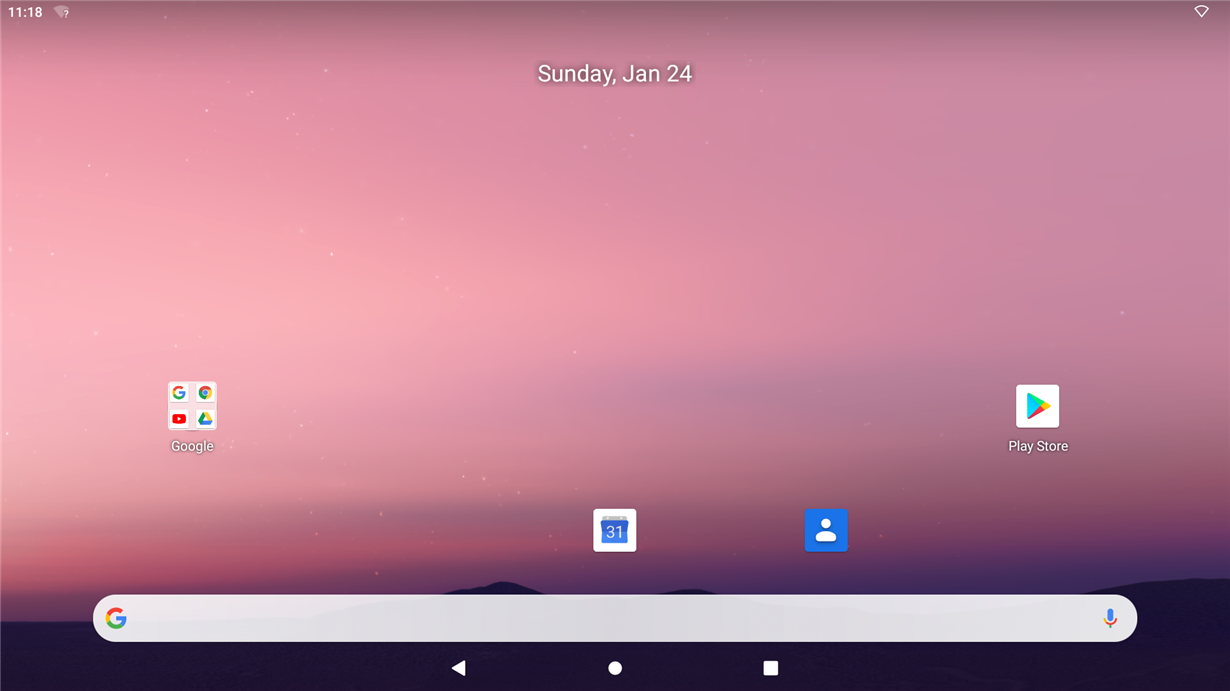

1. Qualcomm output RGB888 + Bridge IC SN65DSI86 output 888 + RGB888 LCD,LCD could appear;

2、 Qualcomm输出RGB888 + Bridge IC output 888 + RGB666 LCD,LCD could appear;

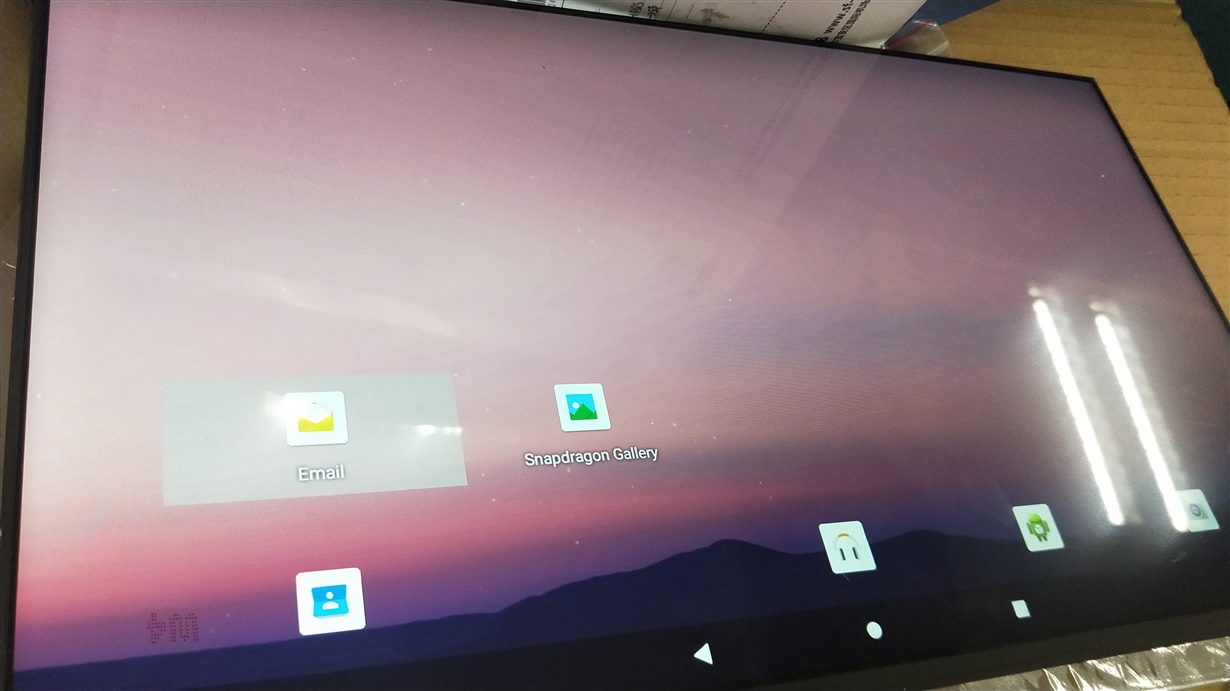

3、 Qualcomm输出RGB888 + Bridge IC output 666 + RGB666 LCD,NG;

4、 Qualcomm输出RGB888 + Bridge IC output 666 + RGB888 LCD,NG;

5、 Qualcomm输出RGB666 + Bridge IC output 666 + RGB666 LCD,NG;

So it looks like the 24 bpp DSI input to 18bpp eDP output conversion failed. Could you please help to analysis?

Best regards

Kailyn