How much is the actual input jitter tolerance for PCLK using external oscillator mode?

I took a look at the datasheet and found a spec, tJIT1 but it said 1T@NOM only.

It does not make any sense to me.

How much is the actual PCLK period allowed with that spec?

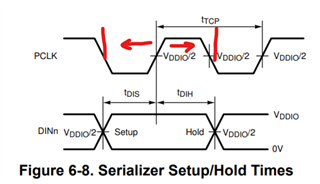

For example, if PCLK is set to 100MHz, which means the tTCP is 10ns and the tJIT1 NOM is also 10ns.

How much are the allowable/expected maximum/minimum PCLK periods?

Max ?[ns]

Min ?[ns]