Part Number: DP83848K

HI,Friend,

My PHY device is DP83848KSQ,I operate the Ethernet Compliance Testing for it.

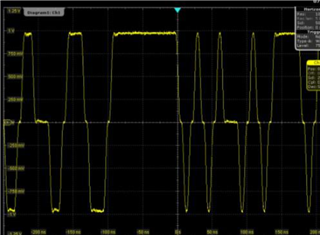

In order to generate idle waveform for Compliance Testing,I used USB-to-MDIO to write 0x2100 to register 0x00,but the waveform's frequence is biger than the standard,so that it couldn't be tested.

I want to know why and please provide me with some advice or document about this test.

THANKS,

Teck.