Other Parts Discussed in Thread: SN65DSI84

After power is applied and stable, How can we let the DSI CLK lanes to be in HS state and let the DSI data lanes be driven to LP11 state?.There is anything we should to do ?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

After power is applied and stable, How can we let the DSI CLK lanes to be in HS state and let the DSI data lanes be driven to LP11 state?.There is anything we should to do ?

Hi Lu,

Your DSI source is what drives the DSI lanes. You will need to consult with your DSI source manufacturer for details on how to drive the DSI lanes to LP11 and HS.

Regards,

I.K.

Hi I.K:

Regards,

Chen.Lu

Hi Chen,

1. In test pattern mode the device does not use any input DSI data. It only uses the DSI CLK or optionally an external REFCLK. The clock is used to internally generate the pattern and output it to a display

2. Step 2 and step 8 do not need to be followed in test pattern mode

3. You can try this version of the tool instead: https://tidrive.ext.ti.com/u/5B25JYQduSH2Hbkl/DSI%20Tuner%202.1.zip?l

Regards,

I.K.

Hi I.K:

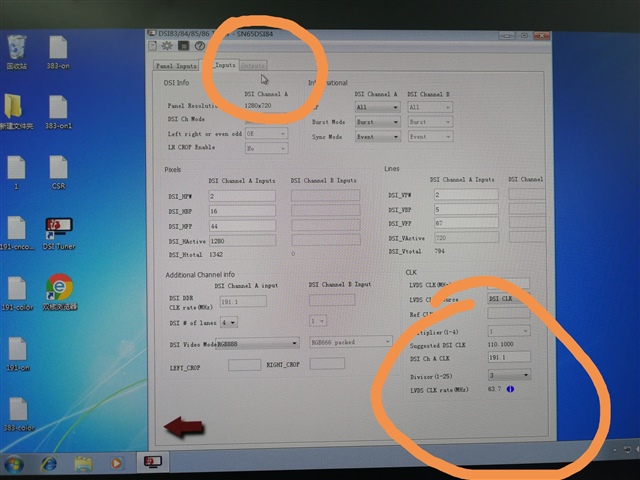

We have screen parameters and use DSI tuner to configure sn65dsi84. But now we have some problems, which are very urgent.

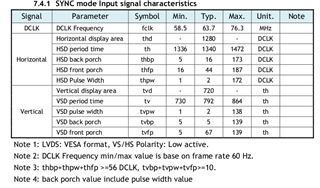

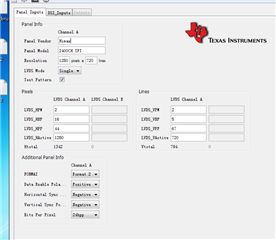

1、we use Flatlink Output Data (Format 2); Single-Link 24 Bpp,Here are our screen parameters.

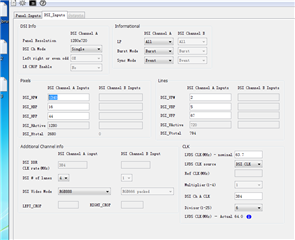

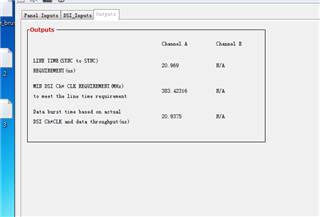

2、The following is our configuration using DSI tuner. In order to make the LVDS line time match the DSI line time, I added DSI_ HPW to 1340. However, after the initialization sequence is completed, register 0xe5 is equal to 0x01. Can you tell me if there is a problem with the configuration, and if so, what is the reason?

3、Here is my initialization sequence

0d 00 0a

09 00 0a

0a 05 00

0b 28 00

10 26 00

11 00 00

12 4c 00

13 00 00

18 78 00

19 00 00

1a 03 00

1b 00 00

20 00 00 /* width-l(a) */

21 05 00 /* width-h(a) */

22 00 00 /* width-l(b) */

23 00 00 /* width-h(b) */

24 d0 00 /* height-l(a) */

25 02 00 /* Height-h(a) */

26 00 00 /* height-l(b) */

27 00 00 /* height-h(b) */

28 b1 00 /* sync delay low(a) */

29 02 00 /* sync delay high(a) */

2a 00 00 /* sync delay low(b) */

2b 00 00 /* sync delay high(b) */

2c 02 00 /* hpw-l(a) */

2d 00 00 /* hpw-h(a) */

2e 00 00 /* hpw-l(b) */

2f 00 00 /* hpw-h(b) */

30 02 00 /* vpw-l(a) */

31 00 00 /* vpw-h(a) */

32 00 00 /* vpw-l(b) */

33 00 00 /* vpw-h(b) */

34 10 00 /* hbp(a) */

35 00 00 /* hbp(b) */

36 05 00 /* vbp(a) */

37 00 00 /* vbp(b) */

38 2c 00 /* hfp(a) */

39 00 00 /* hfp(b) */

3a 43 00 /* vfp(a) */

3b 00 00 /* vfp(b) */

3c 10 00 /* bit4 channel a test pattern; bit0 - channel b test pattern */

3d 00 00

3e 00 00

0d 01 0a

09 01 0a

ff 00 00

e5 ff 0a];

Regards,

Chen.Lu

Hi Lu,

Your settings are not correct - the DSI CLK should be 191.1 MHz. Additionally, the pixel/line settings on the LVDS side must match the pixel/line settings on the DSI side. Please reference this training video to correctly configure the device: https://training.ti.com/configuring-sn65dsi8x-single-channel-dsi-single-link-lvds-operation

Regards,

I.K.