Hello,

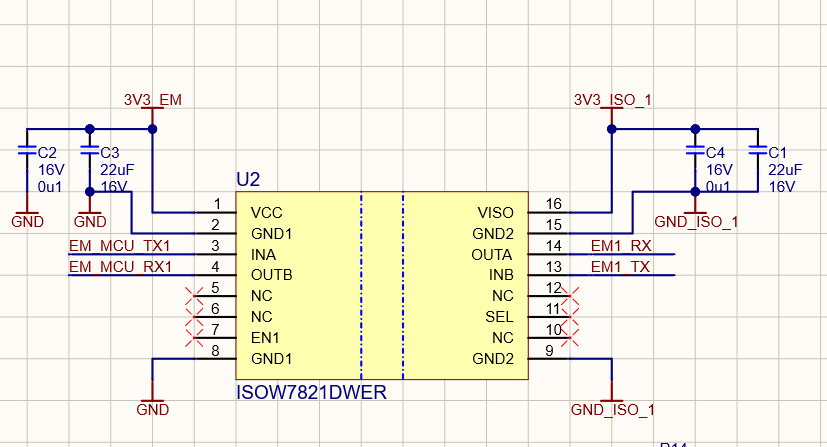

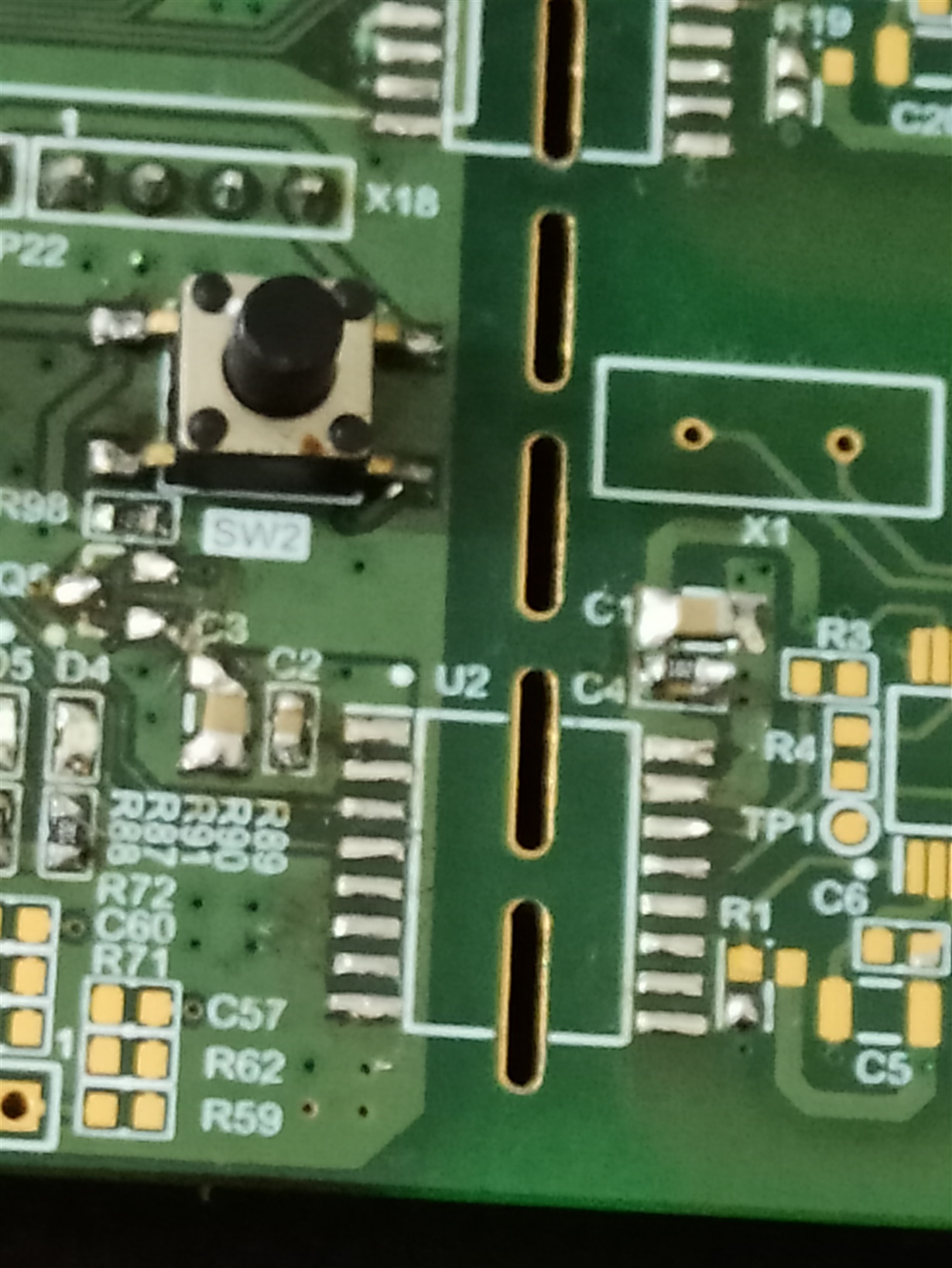

I am trying to use ISOW7821DWER in one of my design, I have connected Input VCC as 3.3v and expect output also as 3.3V but there are two problems:

1. I see a lot of noise introduced to VCC(3.3v) as I connect it to VCC of ISOW7821DWER.(random noise on 3.3V, 500mV peak to peak.

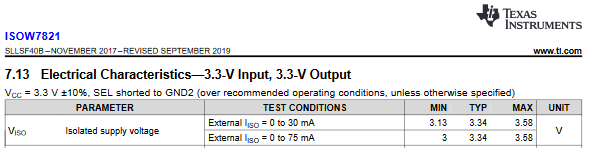

2. Output side(after isolation) I don't get regulated 3.3v but it is like 3.66V, I will I tried putting a 1K resistance as dummy load but it doesn't come down. I will be connected to a metering chip over the UART connection and that will not take more than a few milliamps so I am concerned how can I get ~3.3v output VCC.

I tried putting SEL pin to GND_ISO_1 as well but nothing changes.

Best Regards

Pallav Aggarwal