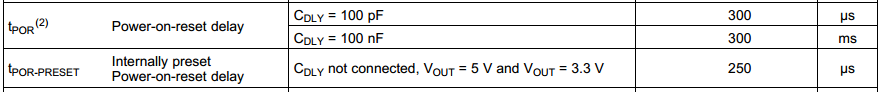

I would like to confirm the duration of tPOR for TPS7A6350-Q1.

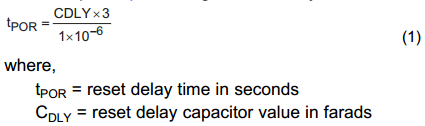

The duration is affected by the vatiation of the capacitor value CDLY.

Are there any items of the duration? How much is the tolerance by IC itself?

I can not find the tolerance (I can find the duration of tWD by ROSC and the tolerance.).

Best regards,

Atsushi Yamauchi