Hi,

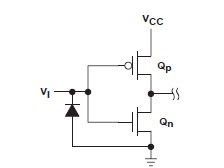

I am performing reliability analysis on a circuit design. One failure mode is the possibility that the input of the SN74LCV1G17-EP Schmitt Trigger is exposed to greater then 6.5 VDC (the maximum specified rating). The datasheet does not specify the input topology, but does indicate that there is no clamping diode from input to VCC. The two over voltage conditions are 15 V current limited by 40kΩ or 7.5 V limited by 10kΩ (375 uA and 750uA respectively). What are the failure modes of the part in this case, does it get stuck high or stuck low?

I suspect there may be a Zener diode on the input to provide ESD protection. If the input current is sufficient to overstress this zener, it may fail short and then the output of the device stuck low. Is this the case?

Is there a failure mode of the input that could cause the device to become stuck high after an overvoltage condition on the input?