Hi expert,

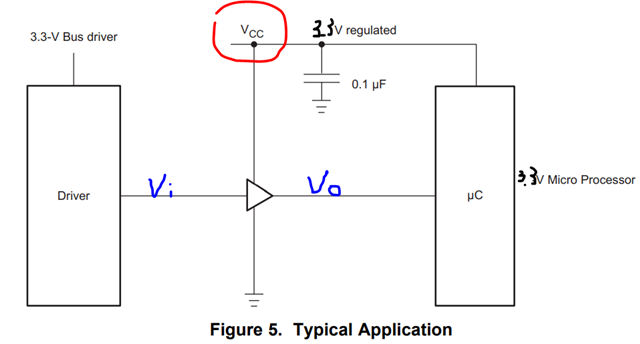

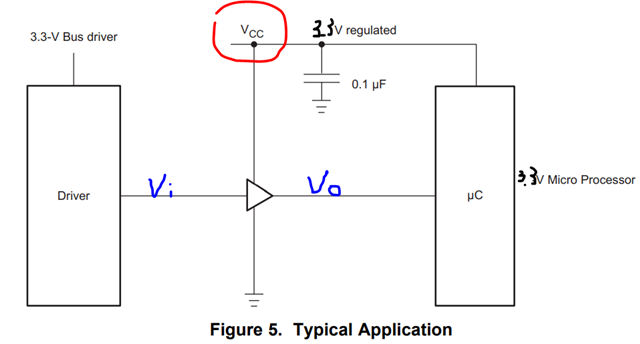

Take below circuit as example.

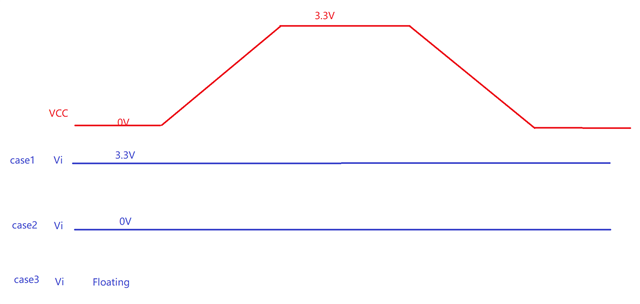

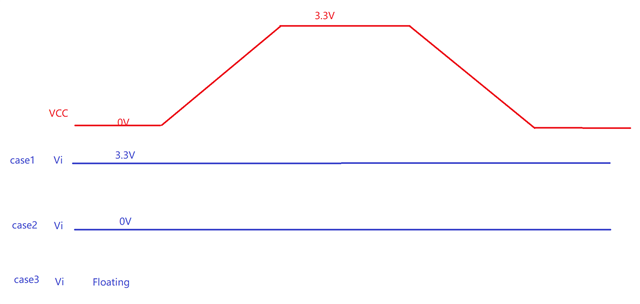

Would like to learn Vo behaviors and waveforms in below three conditions, especially care about: when VDD is very low, internal MOS doesn't work at all, what is the push-pull behavior output of Vo?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi expert,

Take below circuit as example.

Would like to learn Vo behaviors and waveforms in below three conditions, especially care about: when VDD is very low, internal MOS doesn't work at all, what is the push-pull behavior output of Vo?

Hello,

When VCC is set to 0V, this is a defined state, with the outputs being in the high-impedance state, as defined by the Ioff specification in the electrical characteristics table of the datasheet.

The output state is undefined between VCC = 0V and VCC = 0.8V, so I cannot make any guarantees of the operation between those values.

That being said, we would expect the outputs to remain in the high-impedance state until the internal circuitry becomes biased, which would be around 0.5V. After which the device will act like a CMOS buffer.

The output voltage waveforms in the high-impedance state will entirely rely on the output load and parasitics of the system.

Don't leave CMOS inputs floating when the device is powered - more info here: [FAQ] How does a slow or floating input affect a CMOS device?

Understood, thanks for your clear answer.

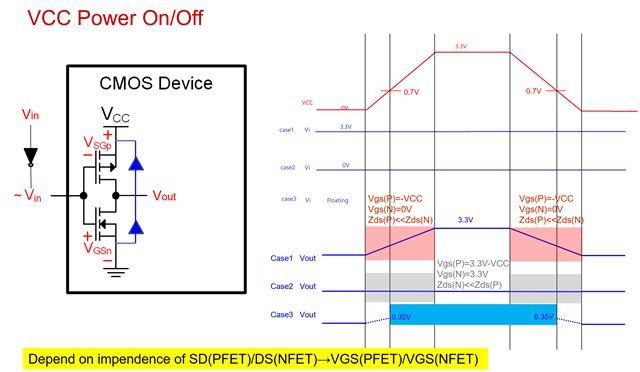

You can check my summary below, I assume CMOS are 3.3V devices, so that Vth=~0.7V.

All components below are ideal and NFET/PFET are totally symmetrical.

And, floating input means Vin = ~ 1/2*Vcc.

Hello,

I'm not sure what the boxed areas are trying to say. Are you trying to check on the state of the output stage of the device when the input is in the 'high' state? How do you know this is true when the device is powered off (no Vcc) or not biased yet (less than 0.5V)?

During the boxed in time, how do you know the output voltage?

When the supply is off, the output is in the High-Impedance state, this is not the same as the low state shown above.

What is driving the output low? If there isn't anything driving the output, how do you know the voltage at that node?

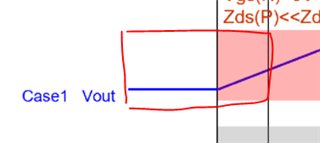

Case 1 output looks more like this:

Case 2 and 3 have similar issues -- the voltage is not 0V, but is unknown during the power-off / high-impedance state. Additionally, if the input is floating, the output will be completely unknown, but will typically be in 1 of 3 states: high, low, or oscillating. I'm not sure how you determined that floating VCC is ~0.5VCC, but in real systems, floating means "unknown" -- ie you can't assign a value to it. The solution is to _not leave the input floating_.

Hi, thank you for your very patient reading and suggestions.

Check my reply below:

I'm not sure what the boxed areas are trying to say. Are you trying to check on the state of the output stage of the device when the input is in the 'high' state? How do you know this is true when the device is powered off (no Vcc) or not biased yet (less than 0.5V)?

Yes I'm trying to check the output state when input is absolute high. I can understand your concern but I'm assuming that my input is 0V or 3.3V enough even if Vcc is not biased yet.

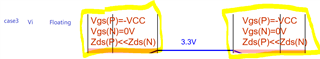

I also make assumption that everything in this CMOS circuit is ideal and NFET/PFET are totally symmetrical, which means no consideration of parasitic and system leakage. That is to say, the divider point "Vout" actually is decided by impendence(I mark "Zds(P)/Zds(N)" here) of PFET and NFET. and the impendence between drain and source actually will be decided by Vgs of CMOS PFET/NFET devices.

Even when Vgs is very low, <Vth, unable to turn on the device channel, but it will affect the effective impendence between drain of source, the leakage resistance is different. That is why you can see an clear output of "Vout" instead of "unknown" in theory. You can verify it in VIRTOSO software.

I'm not sure how you determined that floating VCC is ~0.5VCC, but in real systems, floating means "unknown" -- ie you can't assign a value to it. The solution is to _not leave the input floating_.

I agree with you that I cannot determine floating input is ~0.5VCC, I just assume my input always follow 0.5VCC here for analysis.