Hi team,

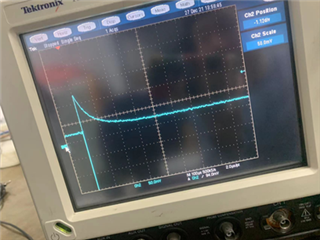

My customer has encountered an issue about the LED flashing when doing the BCI test.

Issue description:

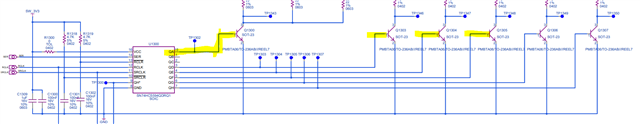

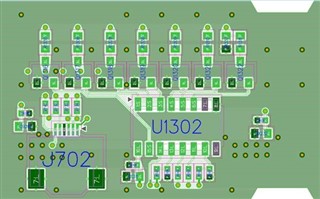

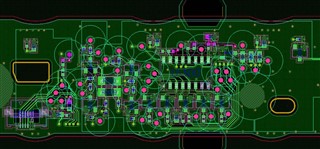

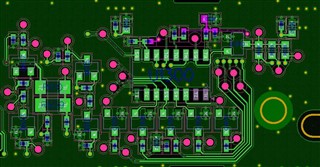

Customer loaded the data into the SN74HCS594-Q1, (all output set to 1), during BCI test we do not modify any data and we see the LED flashing within the range of 110Mhz~200Mhz on different channels (which means some LED still on and some LED channels off). We test 2 boards and both of them happen the issue. We provide all the 1 (high voltage level ) to the input, here is the schematic:

You could see the video below to check the issue phenomenon:

Could you please kindly help to review the customer schematic design by today since they are under EMC test process, if you have any idea of debug this issue, please also provide to us since it is urgent, thank you.