Other Parts Discussed in Thread: SN74LVC1G17, SN74HCS74

The application is Power On/Off button control.

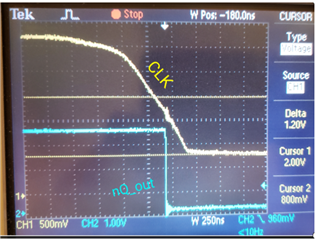

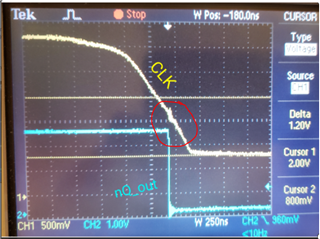

There is R-C delaying circuit on the CLK input which makes the rising and falling edges of the clock slower than the max recommended in the datasheet (at 3.3V) 10ns.

Although the flip-flop works fine at the slow rising CLK edge, it changes its state also when the CLK goes down at almost the same slow rate of 500ns/V.

Is this behaviour expected?

If a comparator is placed on front of the CLK to rectify the slow fall time edge, will it fix the unexpected flip-flop change state?