Other Parts Discussed in Thread: CD4046B, CD74HC4046A

Hi Team,

I have questions about output of PC2_OUT and PCP_OUT.

Attached is the waveform(only PC2_OUT) from the customer system.

I think that these outputs of T0 to T1 and T1 to T2 are correct, but I think that T2 to T3 is not correct.

Here, I think PC2_OUT should be "High impedance" and PCP_OUT should be "High" because SIG_IN and COMP_IN are in the same phase.

However, these outputs remain in pre-state(PC2_OUT is High, PCP_OUT is Low).

Is there anything that you think might be the cause?

My understanding about output of PC2_OUT and PCP_OUT is as follows.

Please let me know if this understanding is wrong.

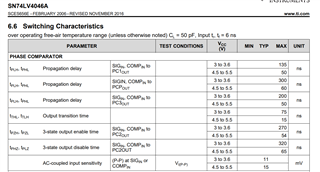

<PC2_OUT>

- This pin is 3-states output.

- A higher frequency at SIG_IN will cause the output to be driven "High".

- A higher frequency at COMP_IN will cause the output to be driven "Low".

- In between these states the output will be in "High impedance".

<PCP_OUT>

- This pin is 2-states output.

- When one of the frequencies of SIG_IN and COMP_IN is higher, it will cause the output to be driven "Low".

- In the other cases, it will cause the output to be driven "High".

Best Regards,