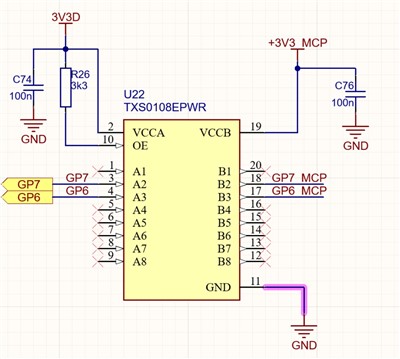

Hi, one of our designs uses TXS0108EPWR as a buffer/power isolator to prevent the A side (ASIC) being damaged/affected when A side is powered off whilst B side is still powered on. Please note both A side and B side are powered at the same voltage level (3.3V) but separate power supplies (3v3D and 3V3_MCP). It has been noticed that if VA is closer or equal to VB (actually VA = VB) the rise time is greatly reduced compared to when there is a difference between the voltage levels of VA and VB. What could be the reason for this? I am not the designer of this, but I will have to implement/design the functionality to do the protection of the A side (ASIC GPIOs) from B side when the ASIC is powered down. B side is a USB Bridge board MCP2210. The design does not use this TXS0108EPWR as a level translator.

Thanks