- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

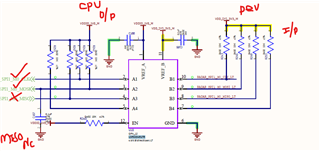

We are using the buffer part LSF0204RUTR in one of our designs for SPI interface As per the design of the buffer we need a Pullup resistor on the O/P to limit the sink current. to the sink capability of the device in VOL limit

Does this requires Pull up on the input as well

the Speed of operation is 1 MHZ

The pull up resistors are currently modified to 600 ohms at the o/p and 300 ohms at the input ..

bus has a cable of 30 mm length after the buffer 32 awg

sink current capability from 1-3 mA

Hi Agxin,

Please help understand LSF will act as a switch and not a buffer and as pull-ups get stronger, VOL increases. You may further see section 5.2 of Voltage-Level Translation With the LSF Family clarifying when pull-ups are needed.

The device will work okay. However, please see TXU0304 for a more suitable buffer for SPI, thanks.

Best Regards,

Michael.

hi thanks for the response

I have calculated the pull up based on the SINK capability in CPU i have set it to 600 ohm and reduced the frequency to 100 khz

after changing it and the spi is working in half duplex mode uni directional

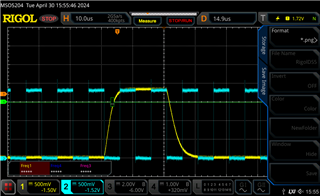

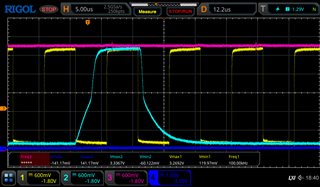

the Clock is proper but the data is having some monotonicity ..The data is raising slowly from the cpu and able to see this at the O/P as well

2 after LT

3 Before LT

Hi Agxin,

The rise is dependent on the pull-ups and the lumped capacitive load. You may use shorter trace and/or disconnect the the line to observe if the load is significant per your desired rise.

See https://www.ti.com/video/5614378694001 and [FAQ] What is the output transition rate for a logic device? further clarifying, thanks.

Best Regards,

Michael.

TXU0304

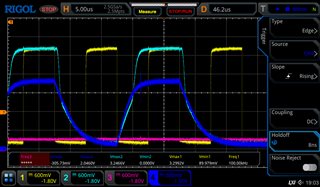

Even with this buffer the data is raising slow at the input .

without the buffer the data is rising fast .. looks like cpu is not capable of having a better slew rate ..

are there any other buffer recommendation with even lower input capacitance