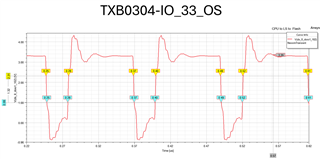

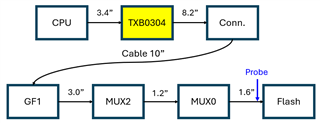

We use TXB0304 to transfer 33MHz and 16MHz CLK from 1V8 to 3V3.

The topology list show as below:

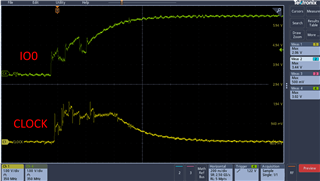

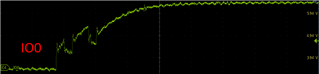

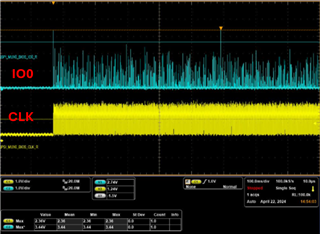

Topology 1: QSPI 16MHz trace length is 14" after level-shift, the waveform of CLK can't be recognized.

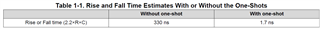

Is there any solution to support topology 1 with trace limitation suggestion? Or how to evaluate topology with small function change

Thank you