As we have the -0.5~4.6V range as the absolute max rating on each signal pin. But it is for long term voltage, which can heat up the esd diode and damage the chip. Since the undershot and the overshot period is short, so normally it will not damage the IC. So do we have any spec can show how high and how long the overshot/undershot spike is, and it will be safe to the IC.

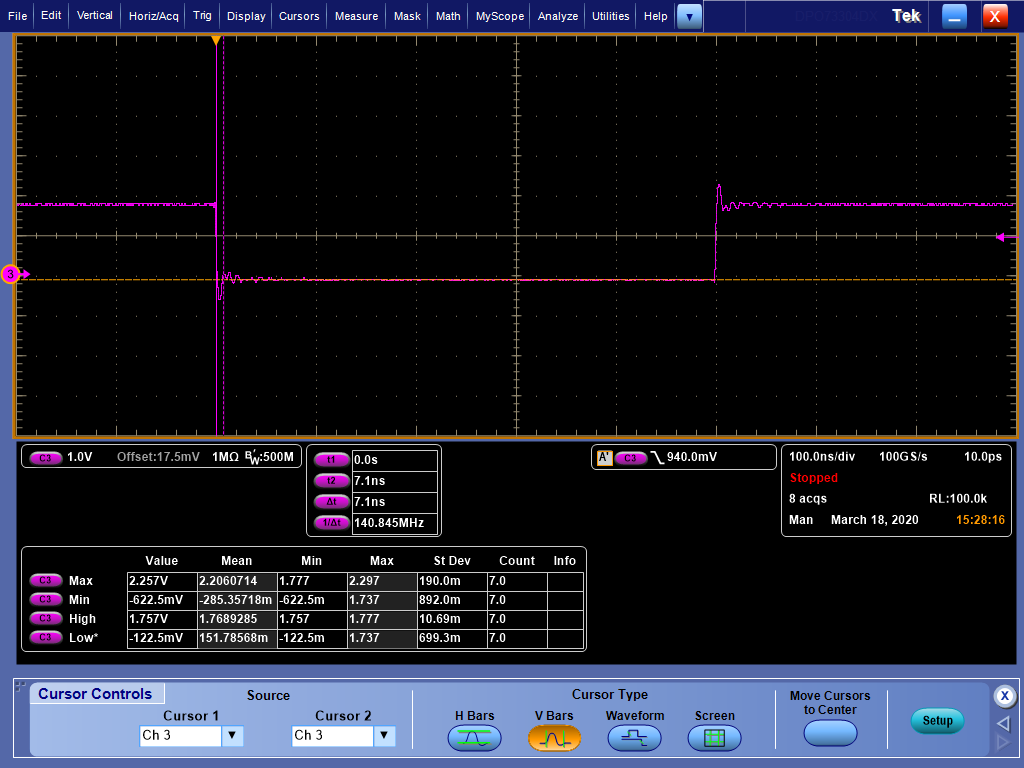

For example, the -0.622V undershot is only 7ns width, will it safe?