Other Parts Discussed in Thread: TXU0104, TXU0202

Tool/software:

Hi Team,

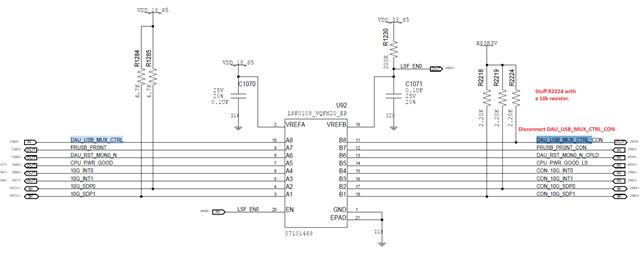

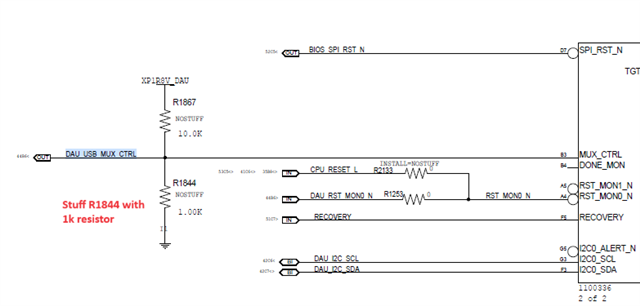

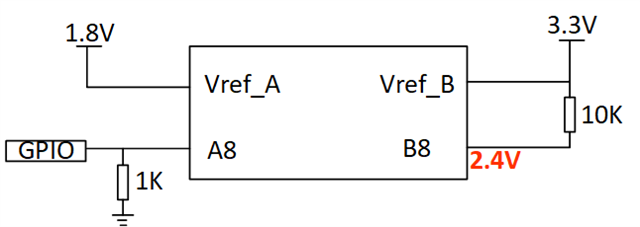

The customer found that when A8 inputs a high level, the high level output by B8 is less than VCCB. Please check the schematic and block diagram below and help analyze the reason? Please note that it seems to be related to the pull-down resistor at A8.

Regards,

Hailiang