- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

H team,

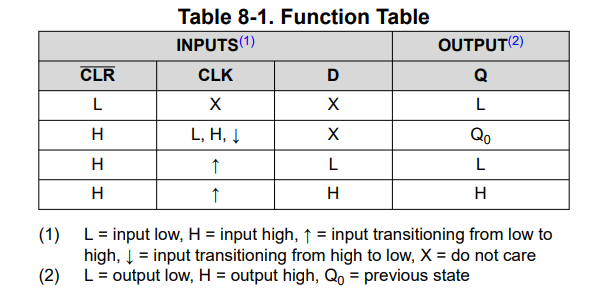

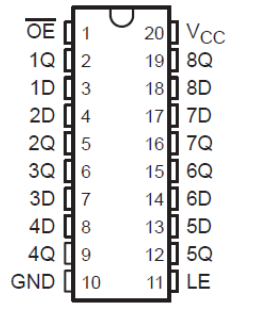

I found that the truth table of SN74LV373A-Q1 are inconsistent with the package pins. Can you help explain what the CLR/CLK represents?

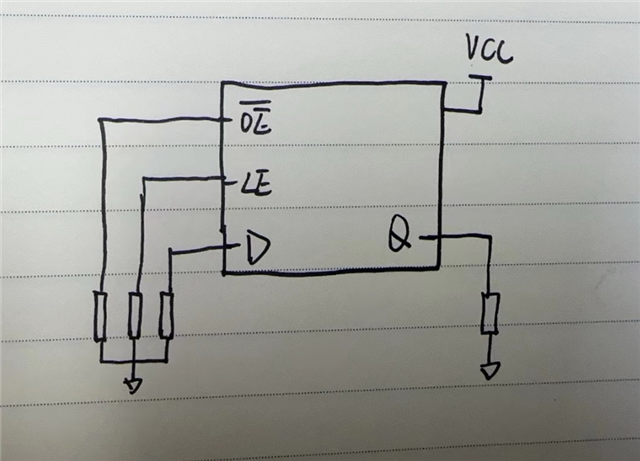

Besides, I connected the devices through the following structures, however, the output is always high, I don't know the reason. We need to latch the output so that the reset of MCU will not influence the output.

Best regards!

Ethan

The function table is wrong; it was accidentally copied from the SN74LV273A-Q1 datasheet. The SN74LV373A datasheet has the correct table.

The initial state of a latch is undefined (either high or low). To get this latch into a known state, you would have to initialize it by pulling LE high with the desired state at the D input.

What is the actual function that you need?

Hi Clemens,

Why I test the initial state of SN74LV373A-Q1 is always high? Does it have some mechanism to latch the output to high in initial state?

Ethan