Tool/software:

Hi Team,

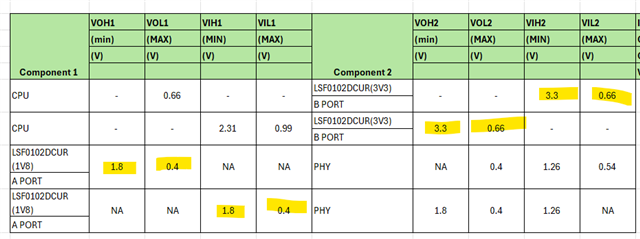

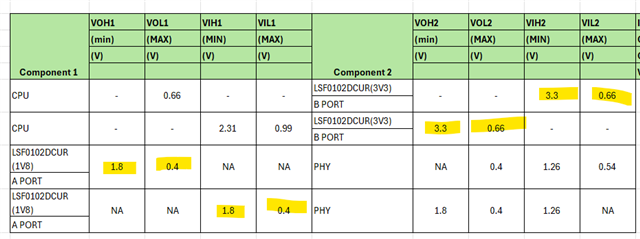

There are no VOH, VIH, VOL and VIL levels.

As these are opendrain supported, can I consider the following levels for electrical compatibility (interfacing with CPU GPIO, MDC, MDIO)?

Thanks,

Vidhya

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi Team,

There are no VOH, VIH, VOL and VIL levels.

As these are opendrain supported, can I consider the following levels for electrical compatibility (interfacing with CPU GPIO, MDC, MDIO)?

Thanks,

Vidhya

The LSF does not have input or output buffers. For voltages below Vref_A, the LSF works as an analog switch. For voltages above Vref_A, the switch is open, and the output voltage is determined by the pull-up resistor.

Please show the schematic, and show the test currents for which the CPU's and PHY's VOL are specified.

Hi Vidhya,

The LSF-type translators do not specify logic threshold levels since no internal buffering circuitry. For VOL, it is dependent on the external pullups used + current that is being sunk into CPU side. Assuming high-Z inputs of downstream device, VOH is near output voltage that the external pullups is biased to.

See Factors Affecting VOL for TXS/ LSF and Logic Minute Videos on LSF for more info.

Regards,

Jack