Tool/software:

Hi Sir,

SPI clock rate around 5MHz

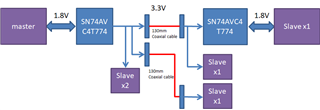

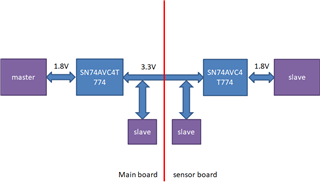

Do you recommend SN74AVC4T774 for the SPI application below?

What should we pay attention to in the application? for example, load capacitance

Do you have any requirements on the input signal of the level shifter? for example, rise time, fall time, etc.

Thanks

Hector