- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

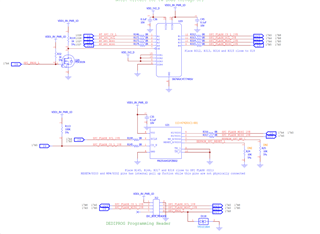

While programming through Dediprog at J12 header, when the system is in OFF condition the VCCA of U19 is at 0V, VCCB at 1.8V (Powered via Dediprog J12 header) and the /OE is 1.8V(since Dediprog pulls SPI_PROG_L net LOW during programming). In this case port B side of U19 the signals are active due to Dediprog programming; Is Port A isolated from port B in this case since VCCA is 0V?

The datasheet says:

The VCC isolation feature ensures that if either VCC input is at GND, then both ports are in the high-impedance state.