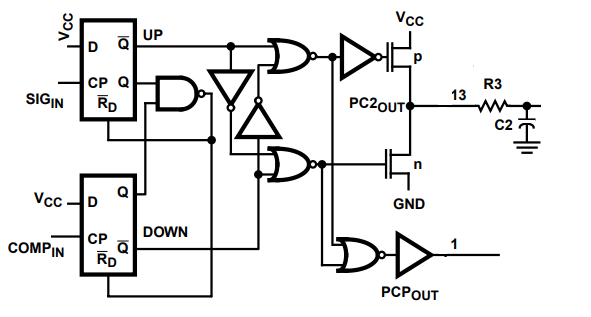

Part Number: CD4046B

Other Parts Discussed in Thread: SN74LV4046A

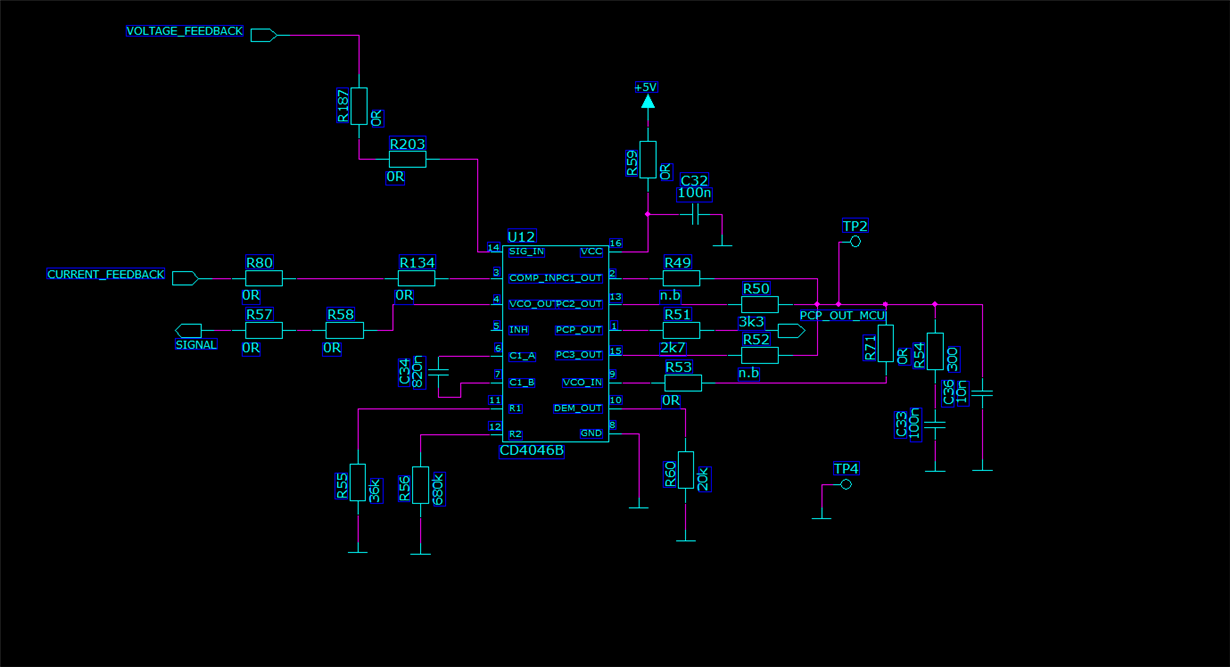

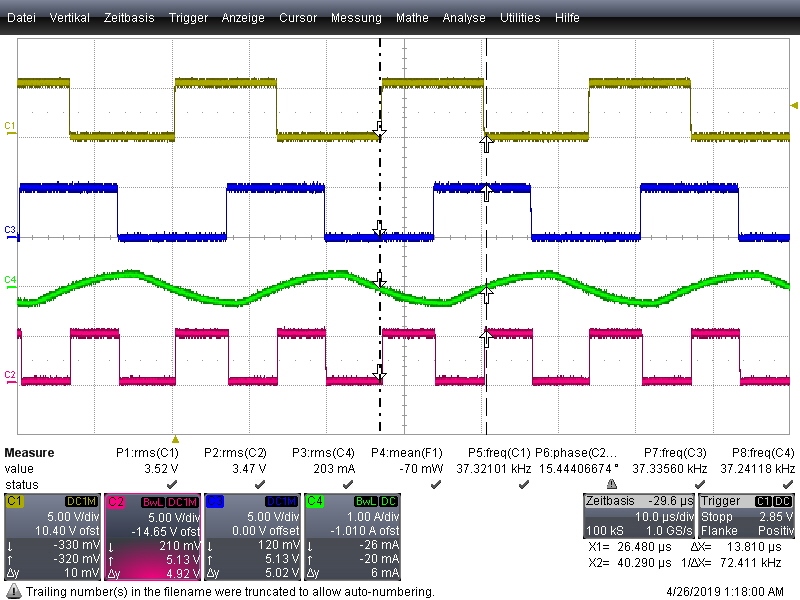

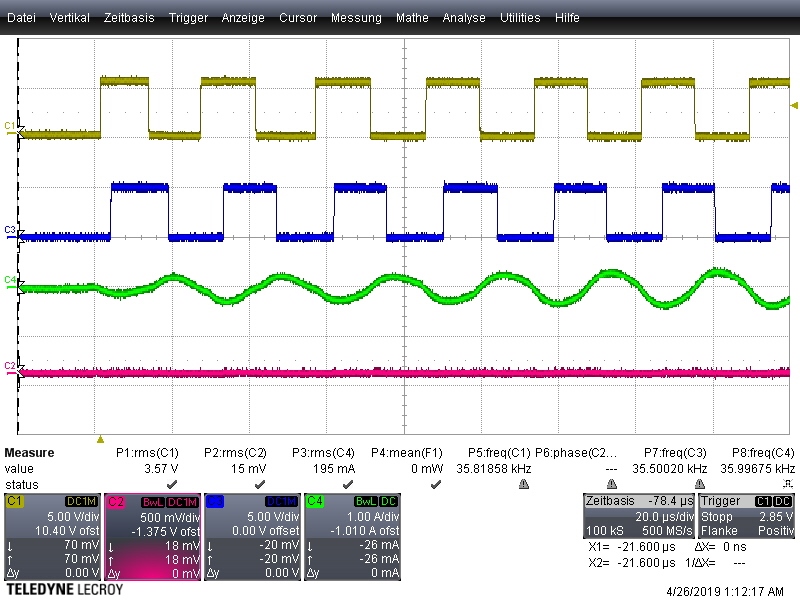

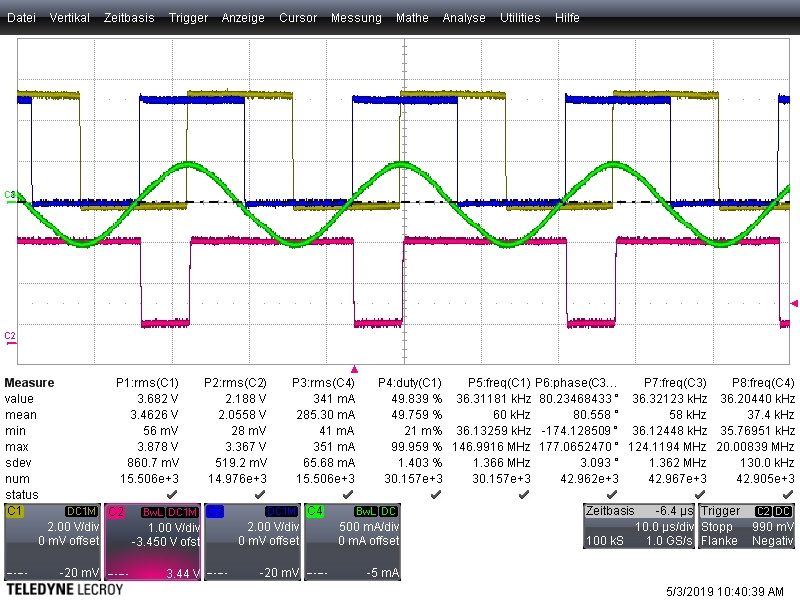

The resistors values used to set the Fmax and Fmin does not produce the same frequency band for different ICs.Is there an way to get the frequency band from fmay to fmin with always the same frequecies with different ICs. My fmin= 35.4kHz and fmax is = 36,6kHz , a bang of 1,2kHz.I am using 680kOhms and 36kOhms resistors with C = 820pF.