Hello,

I have a question regarding the layout of a 4-layer microcontroller board. The board includes a 100 MHz microcontroller, a couple of Sigma-Delta-AD converters (16 bit, 16 SPS) and some little logic devices. I think the latter are generating the highest frequencies on the board (the signal clock speed is low frequency, e.g., 100 kHz, but the edge speed of LVC devices are in the 5 ns range). So I would not call the layout "demanding" with regard to "high speed".

I was looking for best practices on placing routing decoupling capacitors and got confused by obviously contradicting guidelines.

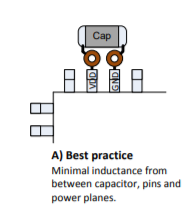

For example the http://www.ti.com/lit/an/spma056/spma056.pdf "System Design Guidelines for the TM4C129x Family of Tiva™ C Series Microcontrollers" recommend this placement routing option as best practice on page 20:

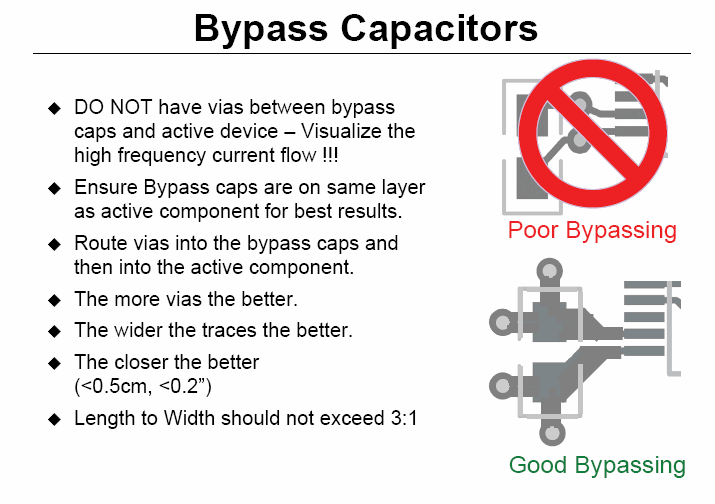

However, the following TI powerpoint http://www.ti.com/lit/ml/slyp173/slyp173.pdf on "high speed design" seems to reject exactly this "best practice" on page 5-23:

I know that the issue of decoupling capacitors is open to discussion, i.e., looking at sources external to TI, one finds even more differing suggestions, e.g., http://www.sigcon.com/Pubs/news/9_07.htm

I understand that when it comes to high speed design (> 1 GHz), one will have to apply simulations to the individual layout to "do it right", however, in the domain of low speed design (< 100 MHz) I expected to find a consensus on "best practices", at least in the TI realm. This seems not to be the case.

I'm a little confused. Please advise. Thanks.