Dear all:

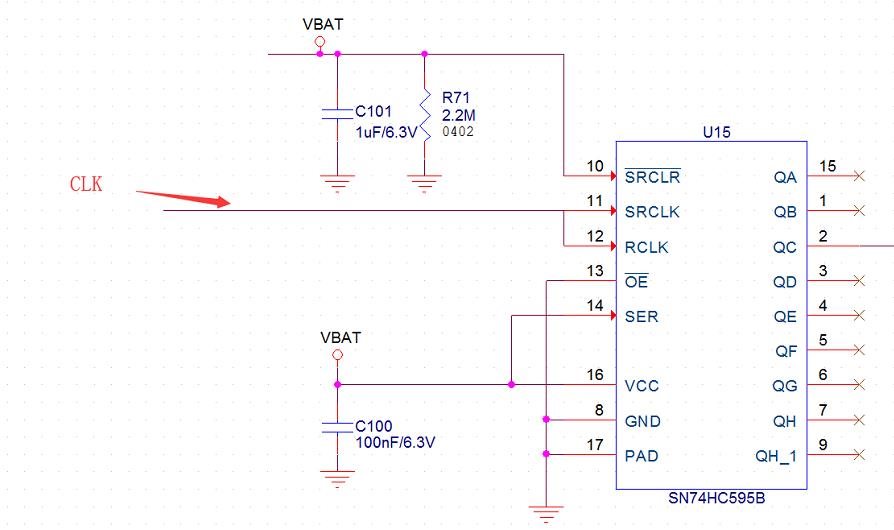

I want to use the following circuit to achieve the flow light control

Now, however, once the CLK is triggered, the output is all high

Did I make any mistakes?Can you give me some advice to realize the water lamp control?

Thank you!

-

I want to use the following circuit to achieve the flow light control