Part Number: TMS570LS3137

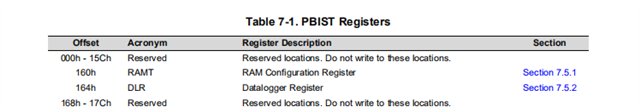

1.According to description in the Chpter 7,"Refer to Table 2-5 for information on the RDS values for each memory." Though the Table 2-5 in the TRM presents the RDS of diffrent RAM Group ,there are no exact information about the meaning of RDS. So, if self-test failed, what's the exact meaning of RDS in the RAM Configuration Register (RAMT)?

2.In the Table 2-5, what's the exact meaning of ESRAM1,ESRAM5,ESRAM6,ESRAM8?Are they the RAM of some module?If so, please tell me the exact module and their corresponding relation. And, Why there are no grouping of TCRAM?

3.As you said,Program Control register is a rsved register. "Resume the test if required using Program Control register(offset = 0x16c) STR = 2." If I want to resume the test, how can I program it?

Thanks.