Other Parts Discussed in Thread: SEGGER, RM46L852

Dear Champs,

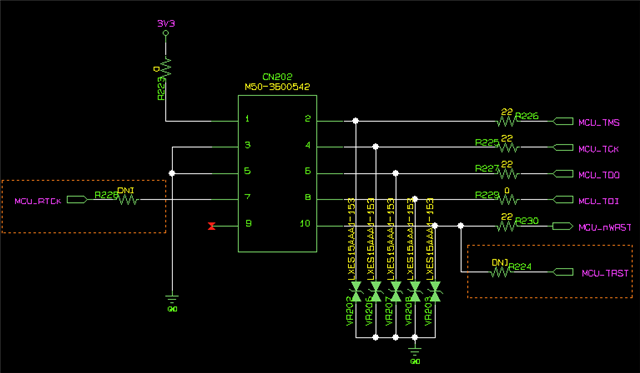

My customer built their custom HW using RM44L520 and 10 pin ARM JTAG connector and faced below errors when they download it using CCS.

They can download only symbols through CCS, and there is no issue to download FW using J-Flash.

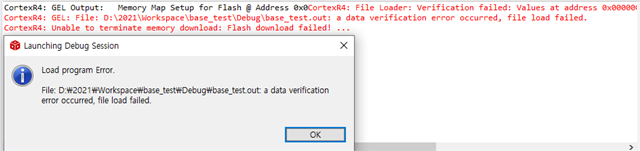

'CortexR4: GEL Output: Memory Map Setup for Flash @ Address 0x0CortexR4: File Loader: Verification failed: Values at address 0x00000000 do not match Please verify target memory and memory map.

CortexR4: GEL: File: D:\2021\Workspace\base_test\Debug\base_test.out: a data verification error occurred, file load failed.

CortexR4: Unable to terminate memory download: Flash download failed! .../

Could you please let me know what should be checked to download FW using CCS?

Their screen shot is as below.

They used RM44L520 GEL file as below.

Their CMD file is as below.

/*----------------------------------------------------------------------------*/

/* sys_link.cmd */

/* */

/*

* Copyright (C) 2009-2018 Texas Instruments Incorporated - www.ti.com

*

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the

* distribution.

*

* Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

* "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

* LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

* A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

* OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

* SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

* LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

* THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

* (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

* OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

/* */

/*----------------------------------------------------------------------------*/

/* USER CODE BEGIN (0) */

/* USER CODE END */

/*----------------------------------------------------------------------------*/

/* Linker Settings */

--retain="*(.intvecs)"

--entry_point=_c_int00

/*----------------------------------------------------------------------------*/

/* Memory Map */

MEMORY

{

VECTORS (X) : origin=0x00000000 length=0x00000020

FLASH0 (RX) : origin=0x00000020 length=0x000FFFE0

STACKS (RW) : origin=0x08000000 length=0x00001800

RAM (RW) : origin=0x08001800 length=0x0000AB00

PROFILE(RW) : origin=0x0800C300 length=0x00007D00 /* Added for profiling purposes */

/*

LOG (RW) : origin=0x08014000 length=0x00002000 fill=0xDEADBEEF*//* Added for logging purposes */

/*FEE (R) : origin=0xF0200000 length=0x00000064 fill=0xDEADBEEF*/ /* For FEE testing, Valid only for sample application */

}

/*----------------------------------------------------------------------------*/

/* Section Configuration */

SECTIONS

{

.excpt_vecs : START( ulFlashStartAddr ) {} > VECTORS

.text : {} > FLASH0

.const : END( ulFlashEndAddr )

{} > FLASH0

.cinit : {} > FLASH0

.pinit : {} > FLASH0

.STACK_DATA_svc : {. += 1024;} > STACKS, RUN_START(StackModeSVC)

.STACK_DATA_fiq : {. += 1024;} > STACKS, RUN_START(StackModeFIQ)

.STACK_DATA_irq : {. += 1024;} > STACKS, RUN_START(StackModeIRQ)

.STACK_DATA_abt : {. += 1024;} > STACKS, RUN_START(StackModeABT)

.STACK_DATA_und : {. += 1024;} > STACKS, RUN_START(StackModeUND)

.STACK_DATA_sys : {. += 1024;} > STACKS, RUN_START(StackModeSYS)

.bss : {} > RAM

.data : {} > RAM

.sysmem : {} > RAM

/* LOG_DATA : START( ulLOGStartAddr ), END( ulLOGEndAddr ) > LOG*/

PROFILE_DATA : START( ulPROFILEStartAddr ), END( ulPROFILEEndAddr ) > PROFILE

}

/*----------------------------------------------------------------------------*/

/* Misc */

/*----------------------------------------------------------------------------*/

Thanks and Best Regards,

SI.