Other Parts Discussed in Thread: TM4C1290NCPDT

I don't have a question, but wanted to provide an possible explanation to an issue raised in the related question (the thread for which is now locked). Perhaps someone from TI can confirm or deny this and provide some detail beyond what is in the data sheet.

Brad Rodriguez (the OP) wrote, "At the moment I am using a TM4C timer to generate a regular 50 usec pulse, triggering on the leading edge, and observing the trailing edge with a digital 'scope. I see about 8 ns of jitter on the trailing edge, of which 2.5 ns can be attributed to the 'scope."

Randy Ott wrote, "I wouldn't be too quick about blaming the PLL for the observed jitter. 8 nS is very close to the 8.333 nS period of the 120 MHz clock... The PLL really should not jitter that much."

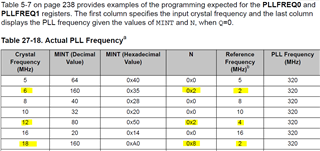

TLDR - I think that the root cause of the jitter is the use of a crystal frequency (25MHz) which is not an exact divisor of 320MHz or 480MHz. I suspect that the jitter would be greatly reduced if any crystal frequency which was an integer divisor were used instead, such as 5MHz, 10MHz, or 16MHz.

Why does the crystal frequency matter? It comes down to how a PLL works, and in this case a fractional-N PLL. A PLL manipulates the voltage which controls the frequency generated by a VCO. It does that by comparing the phase of two signals (one from a reference and one feedback) and making adjustments to keep them phase locked (thus the name "phase locked loop") and thus equal in frequency. To get a higher frequency out of the VCO than the reference (from the crystal, in this case), a frequency divider is inserted into the feedback loop between the VCO output and the phase comparator. If the divider is set to reduce the frequency by 10, for example, the VCO frequency has to be 10X the reference for the divided down version which reaches the phase comparator to equal the reference frequency. So the frequency divider (in the feedback loop) effectively causes the VCO output frequency to be set to a multiple of the reference, in this case 10X. That is all pretty straightforward (in concept), and as Randy wrote, should not result in much jitter on the VCO output.

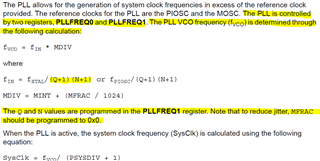

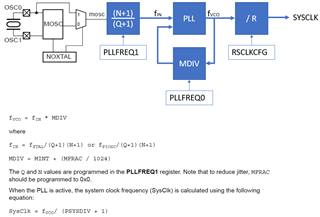

It gets more complicated when you want an output frequency that is some non-integer multiple of the reference. One option is to divide (prescale) the reference frequency before it reaches the phase comparator, then multiply by a larger factor to get the output. I haven't been able to figure out whether the TM4C129 is able to do that or not. If it could, the 25MHz reference could be divided by 5, then multiplied by an integer to reach 320MHz or 480MHz, the frequencies that the VCO supports (which is then divided down to get the 120MHz or whatever system clock). I think that would also give a low-jitter output.

In this case, however, it seems likely to me that a different technique is being used, with a fractional (actually mixed number) divisor in feedback loop, something that is supported by "fractional-N" PLLs. Looking at the source code for _SysCtlFrequencyGet, it looks like there is a /32 (five bit) fraction available (and maybe a /1024). Making up an example with nicer numbers than the real ones, let's say that we had a 16.384MHz crystal (defined as SYSCTL_XTAL_16_3MHZ in sysctl.h) and wanted the VCO to output 320MHz. That means we need a divider ratio of 19.53125 in the feedback loop of the PLL. That happens to be 19 17/32, so it works out perfectly for a /32 fractional-N PLL. Each time a pulse enters the divider, the output either changes or it doesn't; there is no fraction available there. So it divides by 19 some of the time, and 20 the rest of the time (17/32 of the time) so the average divider ratio comes out right. It should now be obvious why there is jitter in the output when using a fractional (rather than whole number) ratio; the divider ratio and therefore the output frequency keeps changing between the available frequency steps (multiples of the reference frequency) to get the desired average frequency.

This variation caused by the changing divider ratio can be smoothed out somewhat by filtering the analog voltage output by the phase comparator before it reaches the VCO so the VCO output doesn't track the changes quite as closely. Search for "PLL loop filter" for more about that (it gets really complicated). In this case, the PLL loop filter is internal to the MCU and can't be changed. But it does affect how closely the output tracks the irregular divider output and therefore makes observations such as the jitter (in the OP's example) of 8nS being close to the 8.333 nS period of the 120 MHz clock less directly related to the divider's operation. I'm not sure if those specific numbers are just coincidence or not, but I am sure that using a fractional divider introduces jitter in the time domain, and corresponding "interesting" (undesirable) effects in the frequency domain.

Whether what I wrote applies in this case is mostly speculation, but it seems to fit the OP's observations and what I have been able to decipher from the source code and datasheet. It would be nice if the TM4C129 datasheet included a block diagram showing the PLL internals with the prescaler (if it has one) and feedback loop dividers shown so we could better explore the tradeoffs and understand the suggested register values.

Steve

P.S. I just stumbled across the Wikipedia page for "dual-modulus prescaler". It appears to work very much like what I described, but is applied to the reference frequency before it reaches the phase comparator. I am not otherwise familiar with such prescalers, but it seems inevitable that they would introduce jitter in a similar way. For all I know, the TM4C129 might have one of these instead of or as well as a fractional-N divider in the feedback loop.