Other Parts Discussed in Thread: RM48L952

Hi,

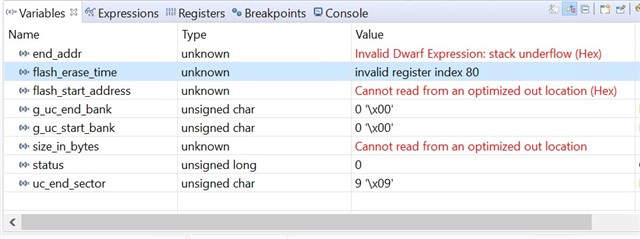

I am trying to erase and program data into the L2FMC Bank 0 and Bank 1 sectors using the library provided. With optimization level O0, seeing that both the operations are successful while using optimization levels O1 and O2, seeing that there is an exception. The operations were performed before enabling the instruction and data caches. Please provide me the solution of how to avoid the dependencies on the optimization level in performing operations on the internal flash. The VCLK used is 180MHz.

Thank you,

Tirumala.