Other Parts Discussed in Thread: TMS570LS3137, TMS570LS1224

Hi,

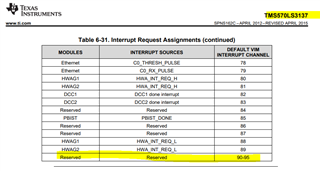

I have certain errors after they occur for multiple times I would want to assert the nError pin by writing to the register. The errors are not present in the ESM group.

On each occurrence of the error I would perform a warm reset and retry the test detecting the error, after certain number error counts I would assert the nError.

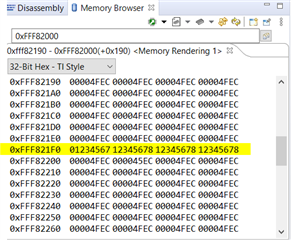

How can I keep track track of the error count after each reset?

Is there any general purpose registers which holds value after reset?