HI,

This is a question regarding High-Integrity bits of DMA module and ESM1.88.

We already checked DMA module section of SPNU563A wasn't described detail about high-Integrity bits.

We would like to identify high-integrity bits of DMA module.

For example, SYS module was described as a following Section 2.5.1.13 of SPNU563A.

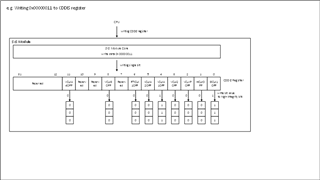

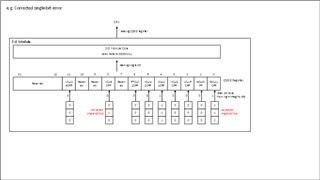

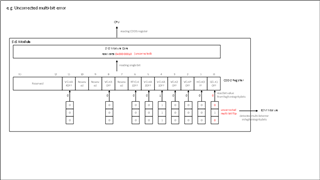

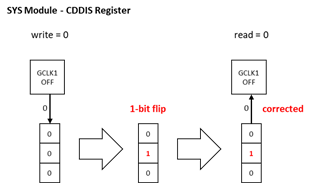

2.5.1.13 Clock Domain Disable Register (CDDIS)

NOTE: All the clock domains are enabled on wakeup.

The application should assure that when HCLK and VCLK_sys are turned off through the HCLKOFF bit, the GCLK1 domain is also turned off.

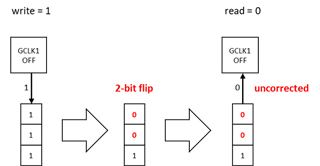

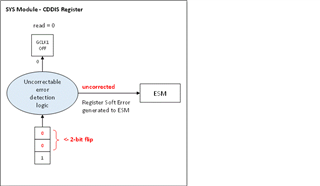

The register bits in CDDIS are designated as high-integrity bits and have been implemented with error-correcting logic such that each bit, although read and written as a single bit, is actually a multi-bit key with error correction capability. As such, single-bit flips within the “key” can be corrected allowing protection of the system as a whole. An error detected is signaled to the ESM module.

Could you please tell me which register corresponds to the high integrity bit.

Thanks,

Sho