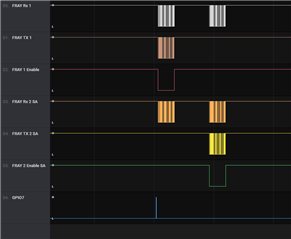

I am using the 6837.TMS570LS3137_FlexRay_Example code provided by TI. I have only 2 nodes on the network. I am monitoring the bus traffic

with a logic analyzer. The two boards come up and transmit the traffic shown in the first picture. Each node alternately transmits and you can see the

message is received on the opposite node's Rx line. This traffic repeats every 5.5 ms. This traffic continues to occur even when the code on one node

is stopped with a breakpoint. I assume this is correct, and this traffic is for synchronization and driven by the state machine hardware. Is this correct?

The short blue pulse on the very bottom trace marks the call to Fr_TransmitTxLPdu after loading data into the WRDS array. No data (except the sync

traffic) is ever transmitted onto the bus by either node. I have NOT changed any of the buffer configuration from the example code. Can you offer some

insight as to why nothing is ever transmitted out on the wire?

Nodes Alternating Tx, top 3 traces belong to node 1, next 3 traces belong to node 2

Traffic pattern repeats every 5.5 ms.

Thank you,

David