Hi,

I have question regarding to CPIOMUX0_INTROUTER0 setting in example: gpio_input_interrupt_am243x-lp_r5fss0-0_nortos_ti-arm-clang

In this example, we are using GPIO1_54 to trigger interrupt to R5FSS0_CORE0 through GPIOMUX_INTROUTER0_OUTP_8.

We using Sciclient_gpioIrqSet( ) to set interrupt router mux.

static void Sciclient_gpioIrqSet(void)

{

int32_t retVal;

struct tisci_msg_rm_irq_set_req rmIrqReq;

struct tisci_msg_rm_irq_set_resp rmIrqResp;

rmIrqReq.valid_params = 0U;

rmIrqReq.valid_params |= TISCI_MSG_VALUE_RM_DST_ID_VALID;

rmIrqReq.valid_params |= TISCI_MSG_VALUE_RM_DST_HOST_IRQ_VALID;

rmIrqReq.global_event = 0U;

rmIrqReq.src_id = TISCI_DEV_GPIO1;

rmIrqReq.src_index = TISCI_BANK_SRC_IDX_BASE_GPIO1 + GPIO_GET_BANK_INDEX(GPIO_PUSH_BUTTON_PIN);

rmIrqReq.dst_id = TISCI_DEV_R5FSS0_CORE0;

rmIrqReq.dst_host_irq = Board_getGpioButtonIntrNum();

rmIrqReq.ia_id = 0U;

rmIrqReq.vint = 0U;

rmIrqReq.vint_status_bit_index = 0U;

rmIrqReq.secondary_host = TISCI_MSG_VALUE_RM_UNUSED_SECONDARY_HOST;

retVal = Sciclient_rmIrqSet(&rmIrqReq, &rmIrqResp, SystemP_WAIT_FOREVER);

if(0 != retVal)

{

DebugP_log("[Error] Sciclient event config failed!!!\r\n");

DebugP_assert(FALSE);

}

return;

}

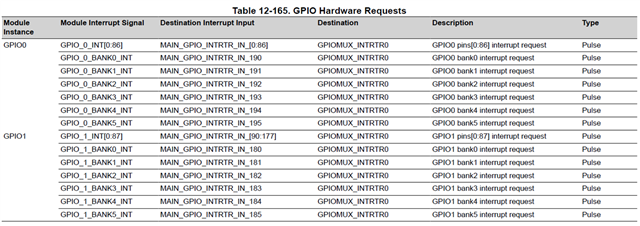

I have question about TISCI_BANK_SRC_IDX_BASE_GPIO1. In the code, we program it to 90U.

/** \brief bank interrupt source index base */

#define TISCI_BANK_SRC_IDX_BASE_GPIO0 (90U)

#define TISCI_BANK_SRC_IDX_BASE_GPIO1 (90U)

#define TISCI_BANK_SRC_IDX_BASE_MCU_GPIO0 (90U)

I'm wondering where is 90U coming from?

I checked TRM, I can not find answer.

Can you please help to clarify? Thanks.

Regards

Andre