Hi champ,

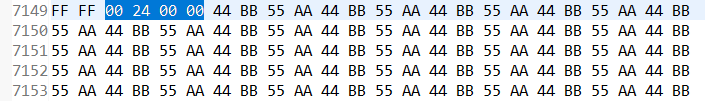

My customer is using F28384S and is facing one CM .const section problem, he splits flash sector 7 into two smaller portions and assigns these two flash portion to .const section in .cmd file.

CMBANK0_SECTOR7_0 : origin = 0x00240000, length = 0x00008000

CMBANK0_SECTOR7_1 : origin = 0x00248000, length = 0x00008000

.const : >> CMBANK0_SECTOR7_0 | CMBANK0_SECTOR7_1, ALIGN(16)

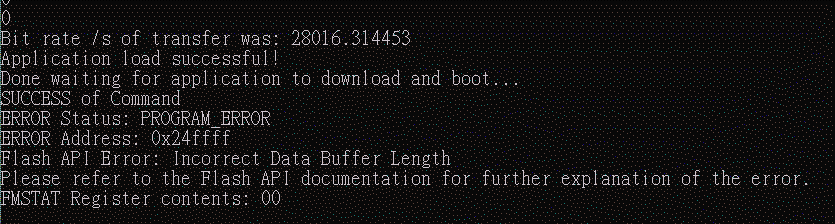

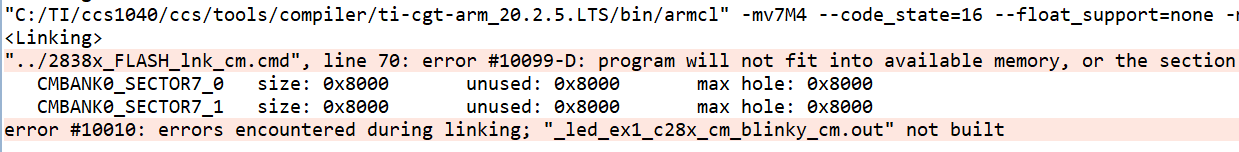

The problem is that when the length of section .const is larger than 0x8000(for example 0x8002), he fails to build the project. The error message is program will not fit into available memory as below,

I am wondering if .const section has any usage restrictions, please advise your comments, thanks for your help.

Regards,

Luke