Part Number: LP-AM243

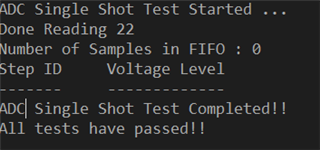

After looking through a lot of the examples such as udma/adc_read and adc/single_shot, I found that pretty much all of the examples listed use the ADC in single shot mode, and have a function that waits for the interrupt to occur before continuing the code. If I switch the adc to continuous mode, naturally with or without the interrupt wait message the code gets stopped after it is told to read.

Do you think it would be possible to have one of the 4 device cores running a continuous ADC to save data to a buffer of sorts, so that a different core can then access that memory at any given time and read the whole buffer? In the linker you can specify memory origin and size so perhaps if I make 2 cores share that memory?

- Thank you for your help.