Hello,

I am currently programming on an AM243x using the MCU+ SDK.

In the past I had asked some questions about interrupt routing,

where the TI guys where a great help.

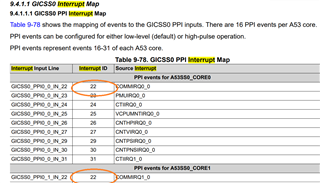

Now I also want to configure the hardwired interrupts.

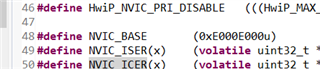

For this purpose I will be using the functionality in kernel/dpl/HwiP.h.

There it says:

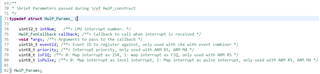

/**

* \brief Parameters passed during \ref HwiP_construct

*/

typedef struct HwiP_Params_ {

uint32_t intNum; /**< CPU interrupt number. */

HwiP_FxnCallback callback; /**< Callback to call when interrupt is received */

void *args; /**< Arguments to pass to the callback */

uint16_t eventId; /**< Event ID to register against, only used with c6x with event combiner */

uint8_t priority; /**< Interrupt priority, only used with ARM R5, ARM M4 */

uint8_t isFIQ; /**< 0: Map interrupt as ISR, 1: map interrupt as FIQ, only used with ARM R5 */

uint8_t isPulse; /**< 0: Map interrupt as level interrupt, 1: Map interrupt as pulse interrupt, only used with ARM R5, ARM M4 */

} HwiP_Params;So, there are some parameters that only apply to a specific MCU.

Especially I would like to use the priorities and the FIQs, as my current concern is having maskable and non-maskable interrupts of different priority.

Here I would like to fail with an ASSERT for instance if an interrupt is set as FIQ but the destination interrupt controller is not the VIM of the R5F-MCU.

But I don't see any way to find out to which destination interrupt controller an interrupt line with the provided IRQ number is connected,

except for the user reading the information from the schematics and providing it as an extra parameter (which could also be a wrong input, which makes the whole assertion obsolete).

I thought I could use HwiP_Config to check at least if the intcBaseAddr is set to that of the R5F-VIM, as said in the comments:

/**

* \brief HwiP config parameters, setup as part of SysConfig, not to be set by end-users directly

*/

typedef struct HwiP_Config_

{

uint32_t intcBaseAddr; /**< For R5F, this is VIM base addr */

} HwiP_Config;to find out if my destination is the R5F-VIM.

But I don't know how to get the HwiP_Config out of the constructed HwiP_Object.

Thank you for your help.

Best regards

Philip.