Other Parts Discussed in Thread: HALCOGEN

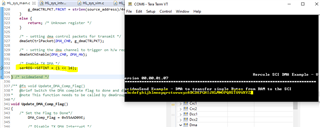

I'd like to set up my SCI to use DMA on transmit, to print stuff without tying up the CPU. At 230400 baud, a character output takes 42 usec, so printing 25 characters takes 1 msec if the CPU polls, as with sciSend().

There was the following discussion about DMA on receive, but I can't tell what was the outcome...

Thanks for all help.