Other Parts Discussed in Thread: SYSCONFIG

Dear Champs,

My customer is using AM2432 ALX package(11x11).

Could you please let me know where detailed document & examples for RAT can be found?

When I checked the TRM, the role of RAT is only translation of address from 48bits to 32bits, but I could not understand why RAT should be used for M4F SS.

Could you please let me know why RAT should be used for M4F SS?

And, Is there usecase need to use RAT with R5 core?

Is there any examples to access peripherals of main domain from M4F SS?

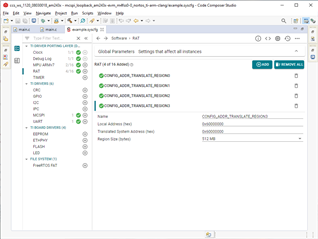

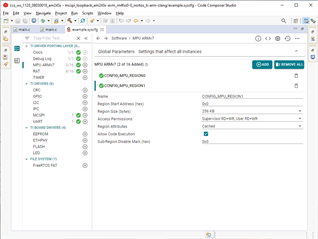

As there is no peripherals of main domain shown in sysconfig for M4F SS as below, it is hard for customer to understand how access on peripherals of main domain from M4F SS.

Please comment your idea on this.

Thanks and Best Regards,

SI.