Hi,

I do have a configuration where, one ADC is being triggered by two different trigger sources. I call them fs1 and fs3. fs1 being 200KHz and fs3 being 1KHz. The source of the triggers are ePWM untis. The input channels of the ADC are used in the following configuration:

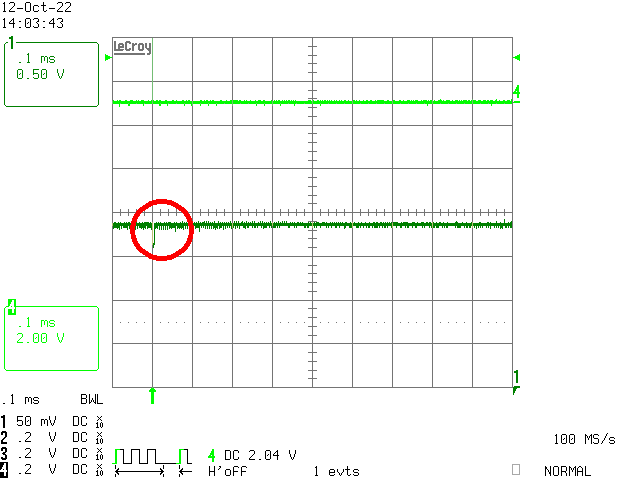

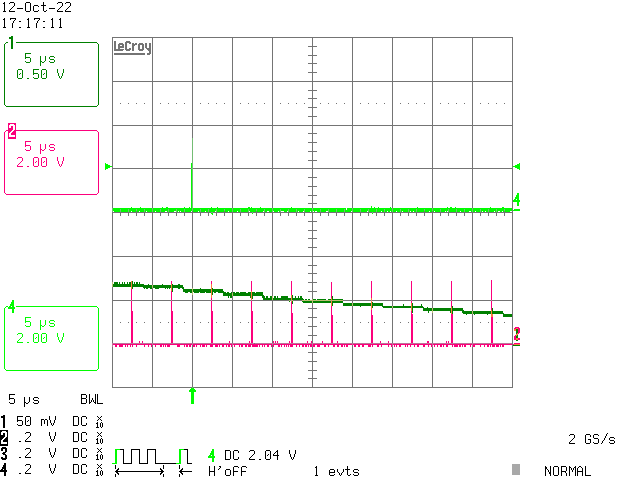

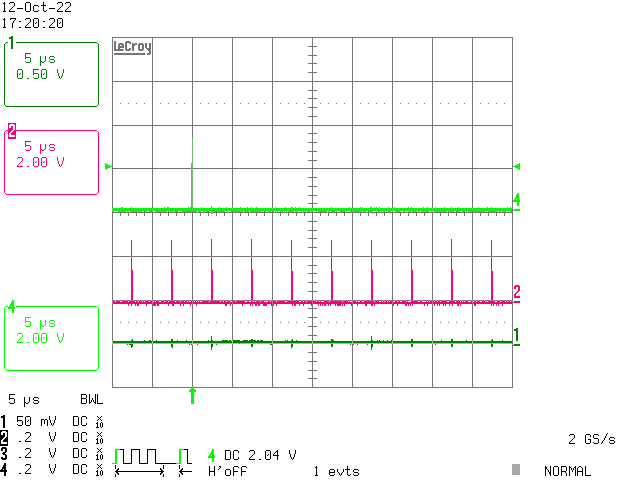

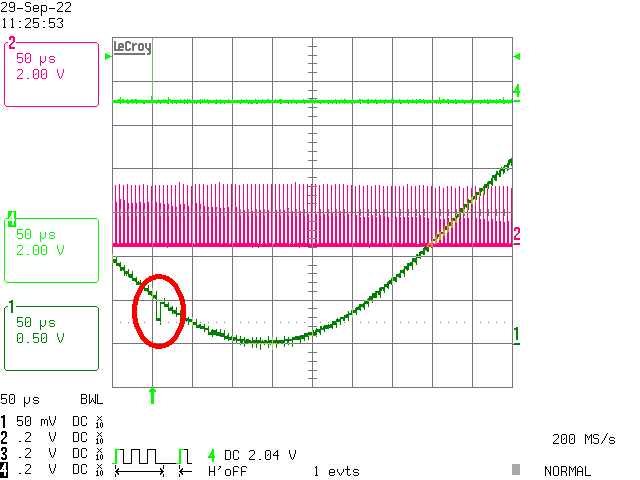

I do apply a SINE WAVE on the CHx inputs and put the converted result back using DMA and the on chip DAC. This works perfect most of the time for all times except channel Ch0. I do use 3 EPWM units to create the triggers (fs1, fs2, fs3) that the ADC's are using. ADC0 shown above is using fs1 to convert the analong input on channel Ch0..Ch2. fs3 is used to convert the remaining channels. Each 1 ms fs1 and fs3 to happen at the very same moment in time - well that's what I assume. The scope shot for the trigger looks the following:

On this shot the input and the three triggers are shown. The triggers are brought to pins in order to capture them as well.

Ch1 --> DAC output

Ch2 --> fs1 (200 KHz)

Ch3 --> fs2 (50 KHz)

Ch4 --> fs3 ( 1 KHz)

As said it works fine most of the except for channel Ch0 of the ADC if fs3 and fs1 do occurr at the same time. The configuration of the ADC trigger is made such that Ch0..Ch2 are in "high priority trigger mode" while channel Ch3..Ch5 are used in the RoundRobin trigger mode.

Looking closer to the DAC output with a slow moing input sine being sampled I do discover a peak or a glitch a do not see for all the other channels being brought to the DAC port. Even if I do remove the sine from Ch0 an short it I do get this glitch then and only then if fs1 and fs3 do happen at the very same time.

The scope shot does show the sine input signal on Ch0 while fs1 and fs3 do happen at the very same moment in time. I do assume it has something to do internally with the trigger priority of the ADC0. Now comes the question

Q: Is there a way I can easily delay the occurrence of fs3 (sourced by an ePWM unit) by lets say 1 usec or so with respect to fs1 (200 KHz) such that it still is 1KHz sampling but guaranteed to happen always 1usec later than fs1?

My assumption is that then it works as expected even for the input Ch0. Because I do never see this behavior for the inputs Ch1 or Ch2 of ADC0 which are converted only a few hundred ns later than Ch0. I do assume maybe a configuration issue for the ePWM units or for the ADC trigger or an internal problem between high-priority trigger and round robin trigger of the ADC itself. I don't know. According to the documentation the 'high-priority-trigger' should win vs the RoundRobin trigger if the triggers do occur within the same clock cycle.

br

Markus