Part Number: AM2434

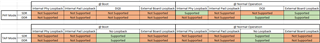

Section "7.10.5.14 OSPI" on the datasheet describes the clocking topologies supported for the receive data capture clock.

I understand the clocking topologies supported in PHY mode as follows:

- Internal PHY Loopback: SDR transfers are supported and DDR transfers are NOT supported.

- Internal Pad Loopback: SDR and DDR transfers are NOT supported.

- External Board Loopback: SDR and DDR transfers are supported.

- DQS: SDR transfers are NOT supported and DDR transfers are supported.

Does AM243x support the Internal Pad Loopback clocking topology?

If only DDR transfers are used in PHY mode, which topology is recommended, External Board Loopback or DQS?

I understand the transfer protocols supported by each of the SPI boot modes (OSPI/xSPI/QSPI/SPI) as follows:

- OSPI Boot: 1S-1S-8S

- xSPI Boot: 1S-1S-1S and/or 8D-8D-8D

- QSPI Boot: 1S-1S-4S

- SPI Boot: 1S-1S-1S

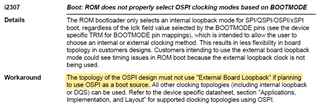

Which data capture mode does each of the SPI boot modes (OSPI/xSPI/QSPI/SPI) operate in, PHY mode or TAP mode?

The transfer protocols supported by boot modes operating in PHY mode must also be supported by the clocking topologies.

Best regards,

Daisuke